# **UltraScale Architecture Memory Resources**

# **User Guide**

UG573 (v1.10) February 4, 2019

# **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02/04/2019 | 1.10    | Added information on common and independent clocks in Address Collision. Revised port A to write port and port B to read port in Simple Dual-Port Block RAM. Removed content clear from UltraRAM Key Features.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 02/09/2018 | 1.9     | Revised description for EN_A and EN_B ports in Table 2-2. Revised Figure 2-16.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11/14/2017 | 1.8     | Revised important note in Common-Clock/Single-Clock FIFO and added note to Set Enable Auto Sleep Mode – EN_AUTO_SLEEP_MODE. Revised UltraRAM Summary. Removed Figure 2-28 and associated verbiage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 08/10/2017 | 1.7     | Added important note to Common-Clock/Single-Clock FIFO. Revised ECC Encode-Only Read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 05/04/2017 | 1.6     | Updated Table 2-5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 03/15/2017 | 1.5     | Revised important note in Block RAM Summary. Added note 2 to Table 1-16. Revised Reset – RST_A, RST_B. Added UltraRAM Timing Diagrams.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 07/20/2016 | 1.4     | Revised Differences from Previous Generations, Synchronous Dual-Port and Single-Port RAMs, Power Saving – RDADDRCHANGE[A B], Power Gating Enable Input – SLEEP, Data-Out Buses – DOUT_A, DOUT_B, Read Status Output – RDACCESS_A, RDACCESS_B, Optional Cascade Register Stage – REG_CAS_[A B], Cascading UltraRAM and Matrix Configurations, and Cascade User Attributes. Added note to Table 1-16 and Table 1-32. Updated Table 2-5. Added AVG_CONS_INACTIVE_CYCLES, MATRIX_ID, NUM_URAM_IN_MATRIX, and NUM_UNIQUE_SELF_ADDR_A B Attributes. Updated Figure 2-1 and Figure 2-5.                                                                                                                                                                                                                                                                                |

| 11/24/2015 | 1.3     | Added UltraScale+ device information. Updated Introduction to the UltraScale Architecture to include UltraScale+ information. Updated important note in Block RAM Summary. Added introductory paragraph to RAMB18/36 Unused Inputs. Reorganized user guide by incorporating previous Chapter 2 (Built-in FIFO) and Chapter 3 (Built-in Error Correction) into Chapter 1, Block RAM Resources, and adding a new Chapter 2, UltraRAM Resources.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 02/24/2015 | 1.2     | Updated Content Initialization – INIT_xx.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 08/14/2014 | 1.1     | Updated bullet 11 in Block RAM Summary. Changed description of CASDINPA[3:0] and CASDINB[31:0] in Table 1-8. Updated description of DOB_REG in Table 1-16. Updated WDADDREN input in Figure 1-6. Added Table 1-14. Updated Cascadable Block RAM. Minor changes in SLEEP and Power Saving – SLEEP_ASYNC. Minor changes to descriptions in Common-Clock/Single-Clock FIFO. Added SLEEP input to Figure 1-21 and Figure 1-22. Added SLEEP port and changed descriptions of CASOREGIMUX, CASOREGIMUXEN, CASDOMUX, and CASDOMUXEN in Table 1-25. Updated Table 1-26. Added Table 1-27. Updated PROG_EMPTY_THRESH, PROG_FULL_THRESH, and REGISTER_MODE in Chapter 1. Removed PROG_EMPTY_THRESH Range for FIFO18E2/FIFO36E2 and PROG_FULL_THRESH Range for FIFO18E2/FIFO36E2 tables in Chapter 2. Updated CASOUTSBITERR, CASINDBITERR, and CASOUTSBITERR in Table 1-8. |

| 12/10/2013 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# **Table of Contents**

| Revision History                                                 | • • • • • • • • | 2   |

|------------------------------------------------------------------|-----------------|-----|

| Chapter 1: Block RAM Resources                                   |                 |     |

| Introduction to the UltraScale Architecture                      |                 | . 5 |

| Block RAM Summary                                                |                 | . 6 |

| Differences from Previous Generations                            |                 | . 9 |

| Block RAM Introduction                                           |                 | 10  |

| Synchronous Dual-Port and Single-Port RAMs                       |                 | 10  |

| Additional Block RAM Features                                    |                 | 17  |

| Block RAM Library Primitives                                     |                 | 27  |

| Block RAM Port Signals                                           |                 | 31  |

| Block RAM Address Mapping                                        |                 | 38  |

| Block RAM Attributes                                             |                 | 39  |

| Block RAM and FIFO Placement                                     |                 | 47  |

| Block RAM Initialization in VHDL or Verilog Code                 |                 | 47  |

| Additional RAMB18E2 and RAMB36E2 Primitive Design Considerations |                 | 48  |

| Block RAM Applications                                           |                 | 50  |

| Built-in FIFO                                                    |                 | 51  |

| Built-in Error Correction                                        |                 | 84  |

| Chapter 2: UltraRAM Resources                                    |                 |     |

| UltraRAM Summary                                                 |                 | 91  |

| UltraRAM Key Features                                            |                 | 92  |

| UltraRAM Cascade                                                 |                 | 93  |

| UltraRAM Error Correction Coding                                 |                 | 93  |

| Block RAM and UltraRAM Differences                               |                 | 94  |

| UltraRAM Primitives                                              |                 | 96  |

| UltraRAM Port Names and Description                              |                 | 99  |

| UltraRAM Attributes                                              |                 | 108 |

| Dual Port SRAM Array Operations                                  |                 | 114 |

| Built-in Error Detection and Correction                          |                 | 123 |

| UltraRAM Timing Diagrams                                         |                 | 127 |

# **Appendix A: Additional Resources and Legal Notices**

| Xilinx Resources                        | 136 |

|-----------------------------------------|-----|

| Solution Centers                        | 136 |

| Documentation Navigator and Design Hubs | 136 |

| References                              | 137 |

| Please Read: Important Legal Notices    | 137 |

# **Block RAM Resources**

# Introduction to the UltraScale Architecture

The Xilinx® UltraScale™ architecture is the first ASIC-class architecture to enable multi-hundred gigabit-per-second levels of system performance with smart processing, while efficiently routing and processing data on-chip. UltraScale architecture-based devices address a vast spectrum of high-bandwidth, high-utilization system requirements by using industry-leading technical innovations, including next-generation routing, ASIC-like clocking, 3D-on-3D ICs, multiprocessor SoC (MPSoC) technologies, and new power reduction features. The devices share many building blocks, providing scalability across process nodes and product families to leverage system-level investment across platforms.

Virtex® UltraScale+™ devices provide the highest performance and integration capabilities in a FinFET node, including both the highest serial I/O and signal processing bandwidth, as well as the highest on-chip memory density. As the industry's most capable FPGA family, the Virtex UltraScale+ devices are ideal for applications including 1+Tb/s networking and data center and fully integrated radar/early-warning systems.

Virtex UltraScale devices provide the greatest performance and integration at 20 nm, including serial I/O bandwidth and logic capacity. As the industry's only high-end FPGA at the 20 nm process node, this family is ideal for applications including 400G networking, large scale ASIC prototyping, and emulation.

Kintex® UltraScale+ devices provide the best price/performance/watt balance in a FinFET node, delivering the most cost-effective solution for high-end capabilities, including transceiver and memory interface line rates as well as 100G connectivity cores. Our newest mid-range family is ideal for both packet processing and DSP-intensive functions and is well suited for applications including wireless MIMO technology, Nx100G networking, and data center.

Kintex UltraScale devices provide the best price/performance/watt at 20 nm and include the highest signal processing bandwidth in a mid-range device, next-generation transceivers, and low-cost packaging for an optimum blend of capability and cost-effectiveness. The family is ideal for packet processing in 100G networking and data centers applications as well as DSP-intensive processing needed in next-generation medical imaging, 8k4k video, and heterogeneous wireless infrastructure.

Zynq® UltraScale+ MPSoC devices provide 64-bit processor scalability while combining real-time control with soft and hard engines for graphics, video, waveform, and packet processing. Integrating an Arm®-based system for advanced analytics and on-chip programmable logic for task acceleration creates unlimited possibilities for applications including 5G Wireless, next generation ADAS, and Industrial Internet-of-Things.

This user guide describes the UltraScale architecture memory resources and is part of the UltraScale architecture documentation suite available at: www.xilinx.com/documentation.

# **Block RAM Summary**

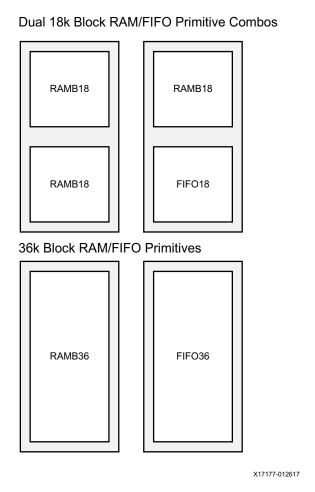

The block RAM in UltraScale architecture-based devices stores up to 36 Kbits of data and can be configured as either two independent 18 Kb RAMs, or one 36 Kb RAM. Each block RAM has two write and two read ports. A 36 Kb block RAM can be configured with independent port widths for each of those ports as 32K x 1, 16K x 2, 8K x 4, 4K x 9, 2K x 18 or 1K x 36 (when used as true dual-port (TDP) memory). If only one write and one read port are used, a 36 Kb block RAM can additionally be configured with a port width of 512 x 72 bits (when used as simple dual-port (SDP) memory). An 18 Kb block RAM can be configured with independent port widths for each of those ports as 16K x 1, 8K x 2, 4K x 4, 2K x 9 or 1K x 18 (when used as TDP memory). If only one write and one read port are used, an 18 Kb block RAM can additionally be configured with a port width of 512 x 36 bits (when used as SDP memory).

Similar to the 7 series FPGA block RAMs, write and read are synchronous operations. The two ports are symmetrical and totally independent, sharing only the stored data. Each port can be configured in one of the available widths, independent of the other port. In addition, the read port width can be different from the write port width for each port. The memory content can be initialized or cleared by the configuration bitstream. During a write operation, the memory can be set to have the data output remain unchanged, reflect the new data being written or the previous data now being overwritten.

#### The block RAM features include:

- Per-block memory storage capability where each block RAM can store up to 36 Kbits of data.

- Support of two independent 18 Kb blocks, or a single 36 Kb block RAM.

- Each 36 Kb block RAM can be used with a single read and write port (SDP), doubling data width of the block RAM to 72 bits. The 18 Kb block RAM can also be used with a single read and write port, doubling data width to 36 bits.

- When used as RAMB36 SDP memory, one port width is fixed (i.e., 512 x 64 or 512 x 72). The other port width can then be 32K x 1 through 512 x 72. When used as RAMB18 SDP memory, one port width is fixed (i.e., 512 x 36). The other port width can then be 16K x 1 through 512 x 36.

- The data outputs of the lower to upper adjacent block RAMs can be cascaded to build large block RAM blocks. Optional pipeline registers are available to support maximum performance.

- One 64-bit error correction coding (ECC) block is provided per 36 Kb block RAM or 36 Kb FIFO. Independent encode/decode functionality is available. ECC mode has the capability of injecting errors.

- Synchronous set/reset of the outputs to an initial value is available for both the latch and register modes of the block RAM output.

- Separate synchronous set/reset pins independently control the set/reset of the optional output registers and output latch stages in the block RAM.

- An attribute to configure the block RAM as a common-clock/single-clock FIFO to eliminate flag latency uncertainty.

- 18, 36, or 72-bit wide block RAM ports can have an individual write enable per byte. This feature is popular for interfacing to a microprocessor.

- Each block RAM contains optional address sequencing and control circuitry to operate as a built-in independent-clock FIFO memory. The block RAM can be configured as an 18 Kb or 36 Kb FIFO.

- All inputs are registered with the port clock and have a setup-to-clock timing specification.

- All outputs have a read function or a read-during-write function, depending on the state of the write enable (WE) pin. The outputs are available after the clock-to-out timing interval. The read-during-write outputs have one of three operating modes: WRITE\_FIRST, READ\_FIRST, and NO\_CHANGE.

- A write operation requires one clock edge.

- A read operation requires one clock edge.

- All output ports are latched or registered (optional). The state of the output port does not change until the port executes another read or write operation. The default block RAM output is register mode.

**RECOMMENDED:** The output datapath has an optional internal pipeline register. Using the register mode is strongly recommended. This allows a higher clock rate. However, it adds a clock cycle latency of one.

The block RAM usage rules include:

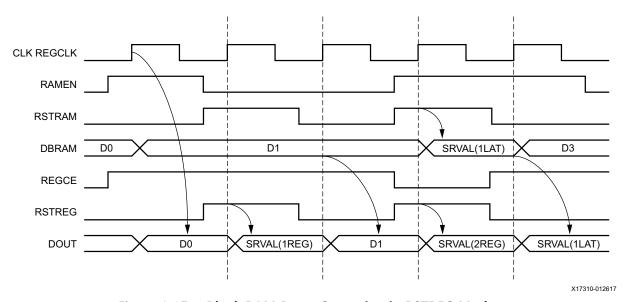

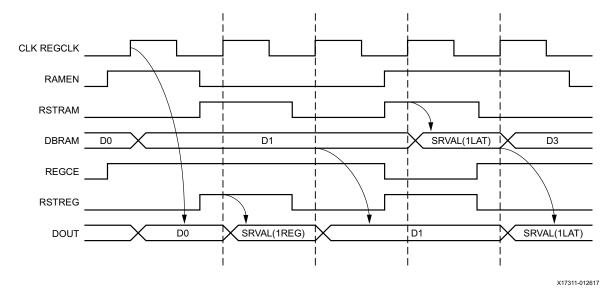

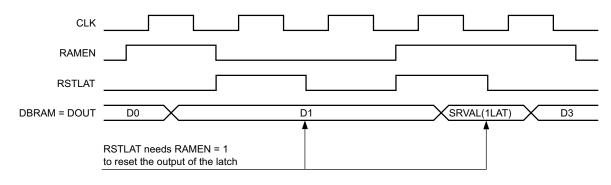

The block RAM synchronous output registers (optional) are set or reset (SRVAL) with RSTREG when DO\_REG = 1. The RSTREG\_PRIORITY attribute determines if RSTREG has priority over REGCE. The synchronous output latches are set or reset (SRVAL) with RSTRAM when DO\_REG is 0 or 1.

**IMPORTANT:** The setup/hold time of the block RAM address and write enable pins must not be violated. Violating the address or write enable setup/hold time (even if write enable is Low) can corrupt the data contents of the block RAM. This most commonly occurs when flip-flops driving block RAM control pins are asynchronously reset, such as a system wide reset. To avoid this issue, design with synchronous resets only for both assertion and deassertion.

- The block RAM register mode RSTREG requires REGCE = 1 to reset the output DO register value if the RSTREG\_PRIORITY is set to REGCE. The block RAM array data output latch does not get reset in this mode. The block RAM latch mode RSTRAM requires the block RAM enable, EN = 1, to reset the output DO latch value.

- There are two block RAM primitives: RAMB36E2 and RAMB18E2.

- Different read and write port width choices are available when using specific block RAM primitives. The parity bits are only available for the x9, x18, and x36 port widths. The parity bits should not be used when the read width is x1, x2, or x4. If the read width is x1, x2, or x4, the effective write width is x1, x2, x4, x8, x16, or x32. Similarly, when a write width is x1, x2, or x4, the actual available read width is x1, x2, x4, x8, x16, or x32 even though the primitive attribute is set to 1, 2, 4, 9, 18, or 36, respectively. Table 1-1 shows some possible scenarios.

**Table 1-1:** Parity Use Scenarios

| Primitive | Sett         | ings         | Effective Read Width | Effective Write Width |  |

|-----------|--------------|--------------|----------------------|-----------------------|--|

| Primitive | Read Width   | Write Width  | Effective Read Width |                       |  |

| RAMB18E2  | 1, 2, or 4   | 9 or 18      | Same as setting      | 8 or 16               |  |

| RAMB18E2  | 9 or 18      | 1, 2, or 4   | 8 or 16              | Same as setting       |  |

| RAMB18E2  | 1, 2, or 4   | 1, 2, or 4   | Same as setting      | Same as setting       |  |

| RAMB18E2  | 9 or 18      | 9 or 18      | Same as setting      | Same as setting       |  |

| RAMB36E2  | 1, 2, or 4   | 9, 18, or 36 | Same as setting      | 8, 16, or 32          |  |

| RAMB36E2  | 9, 18, or 36 | 1, 2, or 4   | 8, 16, or 32         | Same as setting       |  |

| RAMB36E2  | 1, 2, or 4   | 1, 2, or 4   | Same as setting      | Same as setting       |  |

| RAMB36E2  | 9, 18, or 36 | 9, 18, or 36 | Same as setting      | Same as setting       |  |

#### Notes:

1. Do not use parity bits DINP/DOUTP when one port width is less than 9 and another port width is 9 or greater.

# **Differences from Previous Generations**

# **Changes from 7 Series FPGAs**

- When used as SDP memory, all write modes are supported (READ\_FIRST, WRITE\_FIRST, NO CHANGE).

- UltraScale architecture-based devices have a new data cascading scheme. Large block RAMs can now be built in a bottom-up fashion directly in the block RAM column without additional use of logic resources.

- An address enable feature has been added to the block RAM. If disabled, the new address is not latched in the block.

- A dynamic power gating capability has been added. The block RAM can be put into sleep mode while preserving the data content.

- The RAM\_MODE attribute has been removed. The Vivado® tools automatically determine if a block RAM is used in TDP or SDP mode.

- The built-in FIFOs and IP FIFOs have been harmonized as much as possible. This makes it easier to switch between soft and hard FIFO implementations.

- FIFOs allow cascading of multiple FIFO36s and FIFO18s for building deeper FIFOs in hardware.

- A synchronous FIFO reset replacing the asynchronous reset in previous generations has been added.

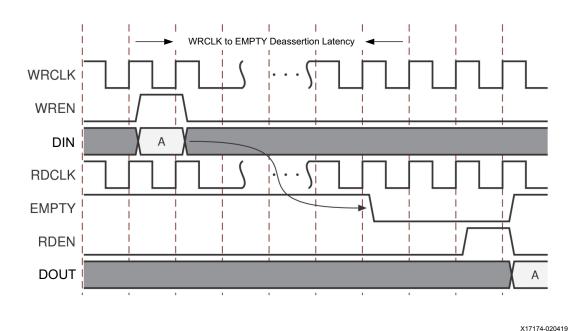

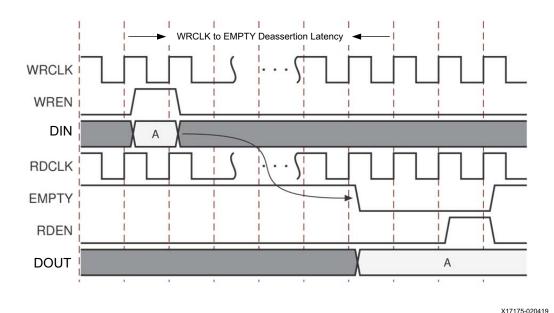

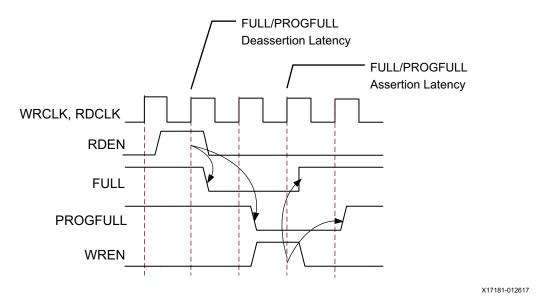

- FIFO latencies of the deassertion of the EMPTY/PROGEMPTY flag for a write operation and the FULL/PROGFULL flag for a read operation have changed.

- The behavior of WRERR and RDERR during reset has changed.

- FIFO asymmetric ports are now supported. The write port and read port can each be configured independently as x4, x9, x18, x36, or x72 for the FIFO36E2, and x4, x9, x18, or x36 for the FIFO18E2.

- The combination of output operating modes (standard and first-word-fall-through) and output register stages configurations has changed.

- WRCOUNT and RDCOUNT now support additional user-selectable functionality.

- The block RAM ECC has additional pipeline registers for improved  $F_{MAX}$ .

- Hardware FIFOs are not backward compatible with 7 series FIFOs.

# **Block RAM Introduction**

In addition to distributed RAM and high-speed SelectIO™ memory interfaces, UltraScale architecture-based devices feature a large number of 36 Kb block RAMs. Each 36 Kb block RAM contains two independently controlled 18 Kb RAMs. Block RAMs are placed in columns within the clock regions (CRs) and across the device. The block RAM data output blocks are cascadable to enable a deeper memory implementation, have a sleep mode for power savings, and have selectable write mode operations.

# **Synchronous Dual-Port and Single-Port RAMs**

#### **Data Flow**

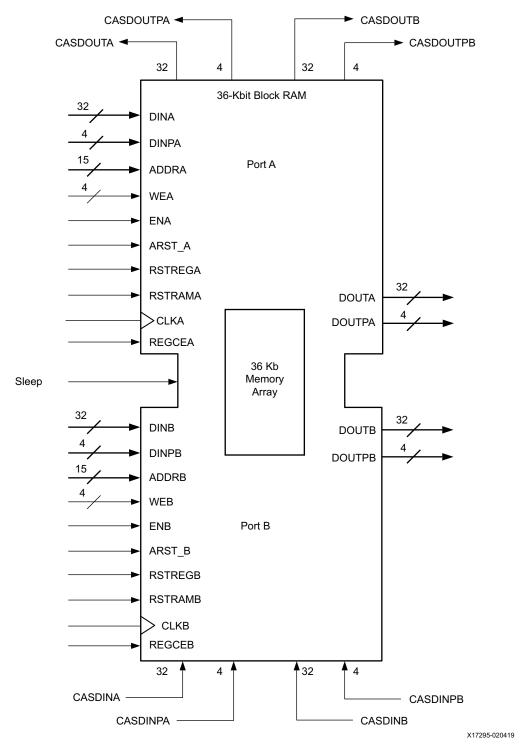

The true dual-port 36 Kb block RAM dual-port memories consist of a 36 Kb storage area and two completely independent access ports, A and B. Similarly, each 18 Kb block RAM dual-port memory consists of an 18 Kb storage area and two completely independent access ports, A and B. The structure is fully symmetrical, and both ports are interchangeable. Figure 1-1 illustrates the true dual-port data flow of a RAMB36. Table 1-2 lists the port functions and descriptions.

Data can be written to either or both ports and can be read from either or both ports. Each write operation is synchronous, and each port has its own address, data in, data out, clock, clock enable, and write enable. The read and write operations are synchronous and require a clock edge.

There is no dedicated monitor to arbitrate the effect of identical addresses on both ports.

**IMPORTANT:** The two clocks must be timed appropriately. Conflicting simultaneous writes to the same location never cause any physical damage but can result in data uncertainty.

Note: The Vivado tools automatically determine if a block RAM is used in SDP or TDP mode.

Figure 1-1: RAMB36 Usage in a True Dual-Port Data Flow

Table 1-2: True Dual-Port Functions and Descriptions

| Port Function  | Description                                                                                                                   |

|----------------|-------------------------------------------------------------------------------------------------------------------------------|

| DIN[A B]       | Data input bus.                                                                                                               |

| DINP[A B] (1)  | Data input parity bus. Can be used for additional data inputs.                                                                |

| ADDR[A B]      | Address bus.                                                                                                                  |

| ADDREN[A B]    | Address latching enable. If Low, the old address is latched.                                                                  |

| WE[A B]        | Byte-wide write enable.                                                                                                       |

| EN[A B]        | When inactive, no data is written to the block RAM and the output bus remains in its previous state.                          |

| RSTREG[A B]    | Synchronous set/reset of the output registers (DO_REG = 1). The RSTREG_PRIORITY attribute determines the priority over REGCE. |

| RSTRAM[A B]    | Synchronous set/reset of the output data latches.                                                                             |

| CLK[A B]       | Clock input.                                                                                                                  |

| DOUT[A B]      | Data output bus.                                                                                                              |

| DOUTP[A B] (1) | Data output parity bus. Can be used for additional data outputs.                                                              |

| REGCE[A B]     | Output register clock enable.                                                                                                 |

| CASDIN[A B]    | Cascade data input bus.                                                                                                       |

| CASDINP[A B]   | Cascade parity input bus.                                                                                                     |

| CASDOUT[A B]   | Cascade data output bus.                                                                                                      |

| CASDOUTP[A B]  | Cascade parity output bus.                                                                                                    |

| SLEEP          | Dynamic shutdown power saving. If SLEEP is active, the block is in power saving mode.                                         |

#### Notes:

- 1. Data-In Buses DINADIN, DINPADINP, DINBDIN, and DINPBDINP, page 34 has more information on data parity pins.

- 2. Block RAM primitive port names can be different from the port function names.

- 3. For a more complete cascade data flow and port descriptions, see Cascadable Block RAM, page 19 and Block RAM Library Primitives, page 27.

# **Read Operation**

In latch mode, the read operation uses one clock edge. The read address is registered on the read port, and the stored data is loaded into the output latches after the RAM access time. When using the output register, the read operation takes one extra latency cycle.

# **Write Operation**

A write operation is a single clock-edge operation. The write address is registered on the write port, and the data input is stored in memory.

#### **Write Modes**

Three settings of the write mode determine the behavior of the data available on the output latches after a write clock edge: WRITE\_FIRST, READ\_FIRST, and NO\_CHANGE. Write mode selection is set by configuration. The write mode attribute can be individually selected for each port. The default mode is WRITE\_FIRST. WRITE\_FIRST outputs the newly written data onto the output bus. READ\_FIRST outputs the previously stored data while new data is being written. NO\_CHANGE maintains the output previously generated by a read operation.

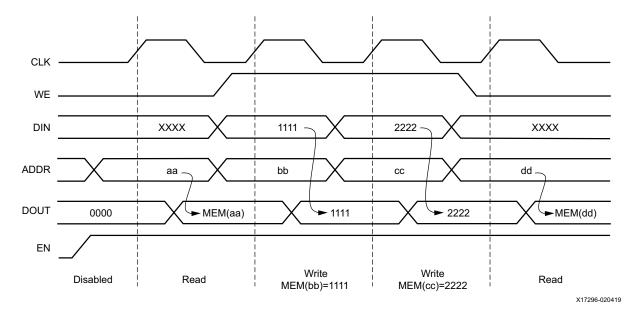

#### WRITE\_FIRST or Transparent Mode (Default)

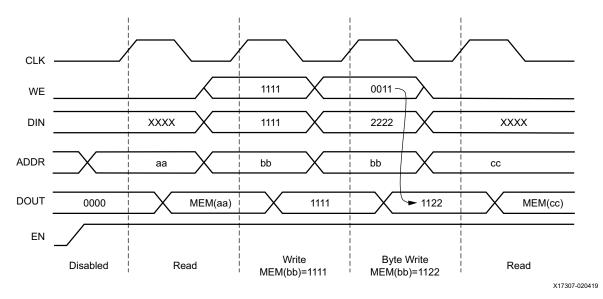

In WRITE\_FIRST mode, the input data is simultaneously written into memory and stored in the data output (transparent write), as shown in Figure 1-2. These waveforms correspond to latch mode when the optional output pipeline register is not used.

Figure 1-2: WRITE\_FIRST Mode Waveforms

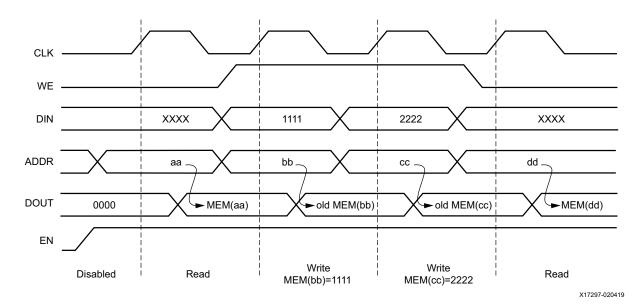

#### READ\_FIRST or Read-Before-Write Mode

In READ\_FIRST mode, data previously stored at the write address appears on the output latches while the input data is being stored in memory (read before write). The waveforms in Figure 1-3 correspond to latch mode when the optional output pipeline register is not used.

Figure 1-3: READ\_FIRST Mode Waveforms

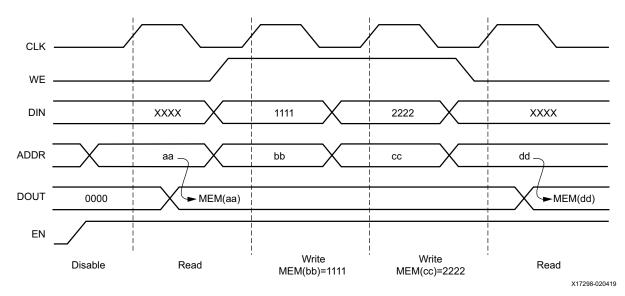

#### **NO\_CHANGE Mode**

In NO\_CHANGE mode, the output latches remain unchanged during a write operation. As shown in Figure 1-4, data output remains the last read data and is unaffected by a write operation on the same port. These waveforms correspond to latch mode when the optional output pipeline register is not used. NO\_CHANGE mode is the most power efficient.

Figure 1-4: NO\_CHANGE Mode Waveforms

#### **Address Collision**

An address collision is when both block RAM ports access the same address location in the same clock cycle. There are two fundamental clock type setups, common clock and independent clock. Common (synchronous) clocks are driven by a common clock buffer driver. All other CLKA and CLKB connections are considered independent (asynchronous) clocks. The CLOCK\_DOMAINS attribute must also be set appropriately. See Table 1-16 for legal and default values. If no address collisions are expected or possible (SDP configurations) to save power, the recommended write mode is NO\_CHANGE. Using READ\_FIRST mode has a 15% power penalty over NO\_CHANGE and should only be used when necessary for functionality or address collision mitigation.

- When both ports are reading, the operations complete successfully.

- When both ports are writing different data, the memory location is written with non-deterministic data.

- When one port is writing and the other port is reading, the write is always successful but the resulting read memory value can vary. See Table 1-3 and Table 1-4.

#### In Table 1-3 and Table 1-4:

- Write enable is active-High, 1 = Write, 0 = Read

- RF = READ\_FIRST, WF = WRITE\_FIRST, NC = NO\_CHANGE

- X = Undeterministic value

- DIA = Port A data input, DIB = Port B data input

Table 1-3: Common Clock

| Clock<br>Type | Write<br>Mode<br>Port A | Write<br>Mode<br>Port B | Write<br>Enable<br>Port A<br>(Data) | Write<br>Enable<br>Port B<br>(Data) | Resulting Data<br>Out Port A | Resulting Data<br>Out Port B | Resulting<br>Memory<br>Value |

|---------------|-------------------------|-------------------------|-------------------------------------|-------------------------------------|------------------------------|------------------------------|------------------------------|

| Common        | RF/WF/NC                | RF/WF/NC                | 0                                   | 0                                   | Old memory data              | Old memory data              | No change                    |

| Common        | RF                      | RF/WF/NC                | 1 (DIA)                             | 0                                   | Old memory data              | Old memory data              | DIA                          |

| Common        | WF                      | RF/WF/NC                | 1 (DIA)                             | 0                                   | DIA                          | X                            | DIA                          |

| Common        | NC                      | RF/WF/NC                | 1 (DIA)                             | 0                                   | No change                    | Х                            | DIA                          |

| Common        | RF/WF/NC                | RF                      | 0                                   | 1 (DIB)                             | Old memory data              | Old memory data              | DIB                          |

| Common        | RF/WF/NC                | WF                      | 0                                   | 1 (DIB)                             | Х                            | DIB                          | DIB                          |

| Common        | RF/WF/NC                | NC                      | 0                                   | 1 (DIB)                             | Х                            | No change                    | DIB                          |

| Common        | RF/WF/NC                | RF/WF/NC                | 1                                   | 1                                   | X                            | Х                            | Х                            |

**Note:** Common clocked access collision is when the port addresses are the same for the same clock cycle.

Table 1-4: Independent Clock

| Clock Type  | Write<br>Mode<br>Port A | Write<br>Mode<br>Port B | Write<br>Enable<br>Port A<br>(Data) | Write<br>Enable<br>Port B<br>(Data) | Resulting Data<br>Out Port A | Resulting Data<br>Out Port B | Resulting<br>Memory<br>Value |

|-------------|-------------------------|-------------------------|-------------------------------------|-------------------------------------|------------------------------|------------------------------|------------------------------|

| Independent | RF/WF/NC                | RF/WF/NC                | 0                                   | 0                                   | Old memory data              | Old memory data              | No change                    |

| Independent | RF                      | RF/WF/NC                | 1 (DIA)                             | 0                                   | Old memory data              | Х                            | DIA                          |

| Independent | WF                      | RF/WF/NC                | 1 (DIA)                             | 0                                   | DIA                          | Х                            | DIA                          |

| Independent | NC                      | RF/WF/NC                | 1 (DIA)                             | 0                                   | No change                    | Х                            | DIA                          |

| Independent | RF/WF/NC                | RF                      | 0                                   | 1 (DIB)                             | Х                            | Old memory data              | DIB                          |

| Independent | RF/WF/NC                | WF                      | 0                                   | 1 (DIB)                             | Х                            | DIB                          | DIB                          |

| Independent | RF/WF/NC                | NC                      | 0                                   | 1 (DIB)                             | Х                            | No change                    | DIB                          |

| Independent | RF/WF/NC                | RF/WF/NC                | 1                                   | 1                                   | Х                            | Х                            | Х                            |

**Note:** An independently clocked access collision might occur when the port addresses are the same and when the clock edges of the two ports are within the same clock cycle. The UNISIM can report an error during simulation for collisions when the SIM\_COLLISION\_CHECK attribute is set to ALL (default).

# **Additional Block RAM Features**

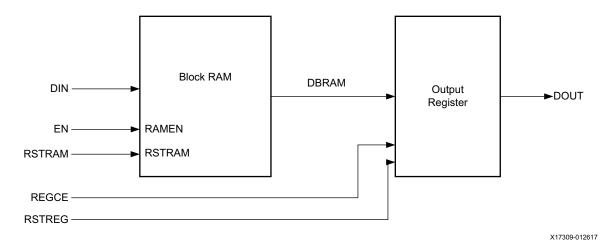

# **Optional Output Registers**

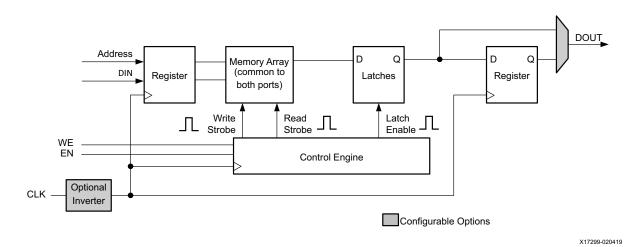

The optional output registers improve design performance by eliminating routing delay to the configurable logic block (CLB) flip-flops for pipelined operation. An independent clock and clock enable input is provided for these output registers. As a result, the output data registers hold the value independent of the input register operation. Figure 1-5 shows the optional output register.

Figure 1-5: Block RAM Logic Diagram (One Port Shown)

# **Independent Read and Write Port Width Selection**

Each block RAM port has control over data width and address depth (aspect ratio). The true dual-port block RAM extends this flexibility to read and write where each individual port can be configured with different data bit widths. For example, port A can have a 36-bit read width and a 9-bit write width, and port B can have an 18-bit read width and a 36-bit write width.

If the read port width differs from the write port width and is configured in WRITE\_FIRST mode, DOUT shows valid new data for all the enabled write bytes. The DOUT port outputs the original data stored in memory for all not-enabled bytes.

Independent read and write port width selection increases the efficiency of implementing a content addressable memory (CAM) in block RAM. This option is available for all UltraScale architecture-based devices true dual-port RAM port sizes and modes.

## Simple Dual-Port Block RAM

Each 18 Kb block and 36 Kb block can also be configured in a SDP RAM mode. In this mode, the block RAM port width doubles to 36 bits for the 18 Kb block RAM and 72 bits for the 36 Kb block RAM. When the block RAM is used as SDP memory, independent read and write operations can occur simultaneously, where port A is designated as the write port and port B as the read port. When the read and write port access the same data location at the same time, it is treated as a collision, identical to the port collision in true dual-port mode. UltraScale architecture-based devices support these modes when the block RAM is used as SDP memory (READ\_FIRST, WRITE\_FIRST, NO\_CHANGE).

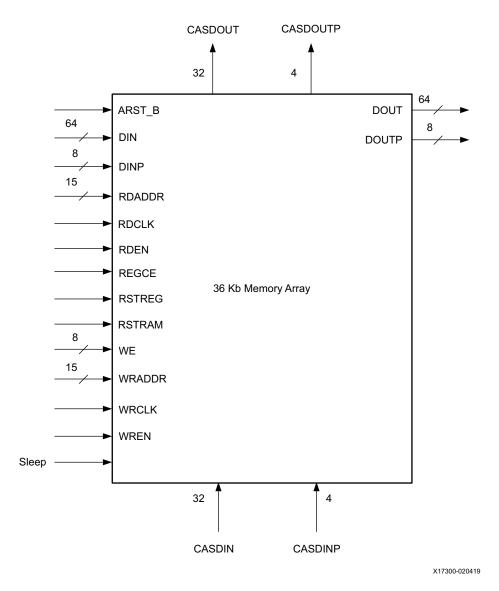

Figure 1-6 shows the simple dual-port data flow for RAMB36 when the block RAM is used as SDP memory.

Figure 1-6: RAMB36 Usage in a Simple Dual-Port Data Flow

Table 1-5 lists the simple dual-port functions and descriptions.

Table 1-5: Simple Dual-Port Functions and Descriptions

| Port Function     | Description                                                                        |

|-------------------|------------------------------------------------------------------------------------|

| DOUT              | Data output bus.                                                                   |

| DOUTP             | Data output parity bus.                                                            |

| DIN               | Data input bus.                                                                    |

| DINP              | Data input parity bus.                                                             |

| RDADDR            | Read data address bus.                                                             |

| RDCLK             | Read data clock.                                                                   |

| RDEN              | Read port enable.                                                                  |

| REGCE             | Output register clock enable.                                                      |

| RSTREG            | Synchronous set/reset of the output registers.                                     |

| RSTRAM            | Synchronous set/reset of the output data latches.                                  |

| WRADDR            | Write data address bus.                                                            |

| WRCLK             | Write data clock.                                                                  |

| WREN              | Write port enable.                                                                 |

| SLEEP             | Dynamic shutdown power saving. If Sleep is High, the block is in power-saving mode |

| CASDIN[A B]       | Cascade data input bus.                                                            |

| CASDINP[A B]      | Cascade parity input bus.                                                          |

| CASDOUT[A B]      | Cascade data output bus.                                                           |

| CASDOUTP[A B]     | Cascade parity output bus.                                                         |

| RDADDREN/WRADDREN | Address latching enable. If Low, the old address is latched.                       |

#### **Notes:**

#### Cascadable Block RAM

UltraScale architecture-based devices provide the capability to cascade data out from one RAMB36 to the next RAMB36 serially to make a deeper block RAM in a bottom-up fashion. The data out cascading feature is supported for all RAMB36 port widths. The block RAM cascade supports all the features supported by the RAMB36E2 module.

**Note:** The 64K x 1 cascade functionality provided in previous architectures has been removed. The same 64K x 1 cascade feature can be achieved using the new cascade block RAM implementation.

The data flow is always from lower block RAM to upper block RAM. All of the signal routings and the control logic for the cascading feature are implemented in hardware. Multiple block RAMs can be cascaded, as required. In cascade mode, a single, common clock source must drive the same block RAM inputs (RDCLK or WRCLK). Furthermore, the data cascade

<sup>1.</sup> For a more complete cascade data flow and port descriptions, see Cascadable Block RAM, page 19 and Block RAM Library Primitives, page 27.

capability allows that the lower RAMB18 of the lower RAMB36 can be independently cascaded to the lower RAMB18 of the upper RAMB36. Similarly, the upper RAMB18 of lower RAMB36 can be cascaded to the upper RAMB18 of the upper RAMB36 site.

**IMPORTANT:** All block RAMs in a cascade chain must have matching configurations for certain features (e.g., common inputs such as the port width must be identical).

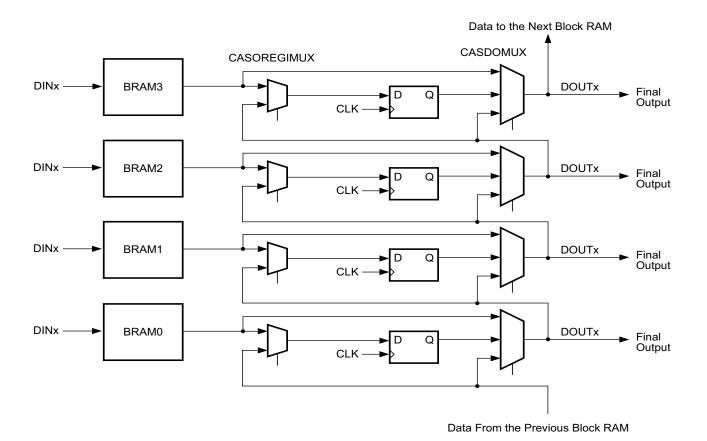

Figure 1-7 shows a high-level, conceptual view of four cascaded block RAMs.

X17301-020419

Figure 1-7: High-level View of the Block RAM Cascade Architecture

The block RAM provides flexibility to support many different implementations of the cascade feature. The three multiplexers (Figure 1-7) that select datapaths and pipeline registers can be dynamically controlled with the input pins.

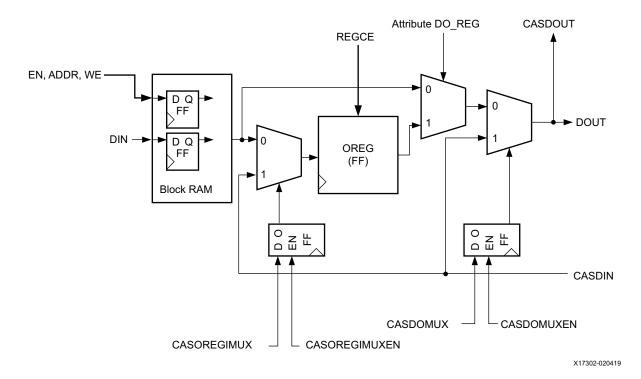

Figure 1-8 shows a more detailed diagram of the functional implementation in a single block RAM block. Three cascade multiplexer selection pins are available when the block RAM is in cascade mode. CASDIMUX selects between either the cascade input data or the direct data input. CASOREGIMUX selects the data output of the block RAM or the cascaded data input to the block RAM's optional output register. This control pin allows pipelined cascading for maximum performance. CASDOMUX selects the data output of the block RAM (with or without the optional register) or the cascaded data input. The latter two cascade multiplexer select pins are registered at the input and have an enable control pin. CASDOUT and CASDIN have dedicated interconnects within a block RAM column. Both the cascade connections and data connection to and from the block RAM are available at the same time.

Figure 1-8: Cascade Functional Diagram

Although many different use cases can be implemented using the block RAM data cascade feature, this chapter describes three of the most common use cases. The examples shown are based on cascading three block RAM blocks, but more block RAM blocks can be cascaded with some limitations as required by the application in the same fashion.

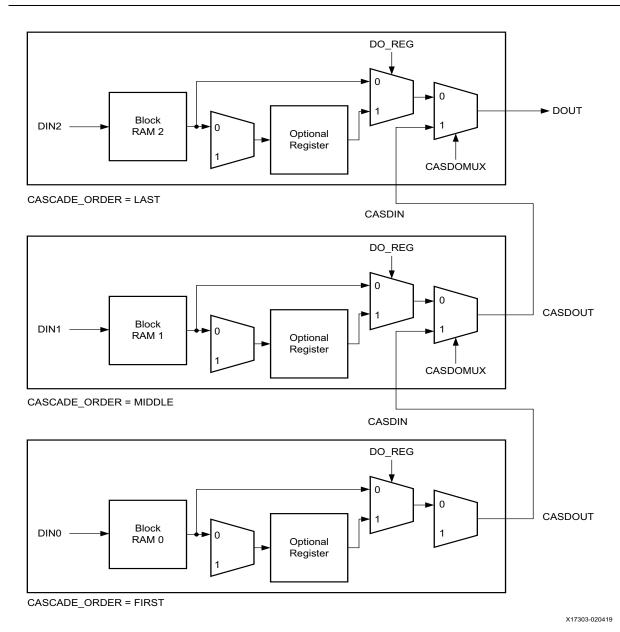

### Standard Data Output Cascade Mode

In this cascade use case, the data out of the lower block RAM is multiplexed to the final output multiplexer of the upper block RAM (Figure 1-9). The cascading can be applied to an entire block RAM column. This case yields a very deep RAM that can be implemented using only a few logic resources that might be required to drive the EN pins, drive the pins of the block RAM, determine the correct select value for the cascade muxes, and align the data if

the DO\_REG is used. The input multiplexer always selects DIN to write to the block RAM, the block RAM output multiplexer always selects the block RAM output data, and the last output multiplexer selects the current block RAM data (optionally registered) or the cascaded data from the block RAM below. The length of the block RAM chain impacts the final clock-to-out performance, which might slow down the performance depending on how many block RAMs are cascaded. All features of the block RAM are supported.

**IMPORTANT:** The attribute CASCADE\_ORDER defines the placement sequence within a block RAM column while the DO\_REG attribute turns the optional block RAM register on or off.

Figure 1-9: Block RAM Cascade – Standard Data Out Cascade

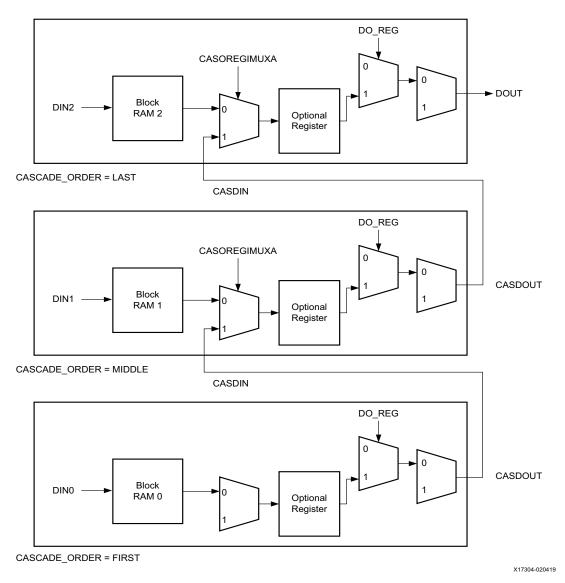

#### Data Out Cascade in Pipeline Mode

The block RAM pipeline cascade mode is similar to the standard data output cascade mode but allows the application to use the cascade mode at higher frequencies (Figure 1-10). The cascading data output propagates through the regular block RAM output registers because they are used as additional pipeline stages to achieve higher frequencies in this cascade mode. The external CASOREGIMUX pin controls the multiplexer that selects the input to the optional register. Thus, the data from the block RAM below or the current block RAM can be stored into the output register. The input multiplexer always selects DIN to write to the block RAM, the block RAM output multiplexer selects the block RAM output data, or the cascaded data from the block RAM below to write to the register. The final output multiplexer for each of the cascade stages always selects the data from the register for the final output data. All the DO\_REG attributes have to be set to TRUE in this case. In this cascading mode, the length of the cascade chain is limited to within one clock region.

Figure 1-10: Block RAM Cascade - Pipelined Data Out Cascade

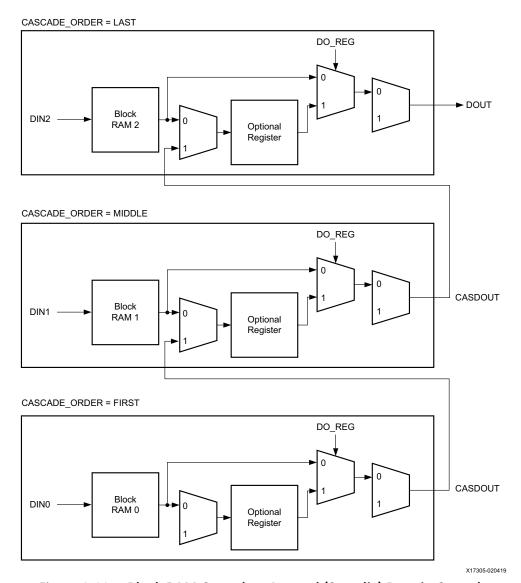

#### Data in Cascade for a Block RAM Array Matrix (Systolic) Mode

The block RAM systolic mode allows an application to write input data or cascaded data into a block RAM (Figure 1-11). At a later cycle, the application can then select to read data from a lower block RAM and write into the next upper block RAM. Data can be read from any dynamically selected block RAM in the cascade chain. The input multiplexer dynamically selects the DIN data or the cascaded data output from the lower block RAM to write to the current block RAM. The block RAM output multiplexer always selects the block RAM output data that is then presented on the data output directly or via the optional register. The DO\_REG attribute determines if the optional register is used. In this cascade mode, the length of the cascade chain is limited to within one clock region.

Figure 1-11: Block RAM Cascade – Arrayed (Systolic) Data in Cascade

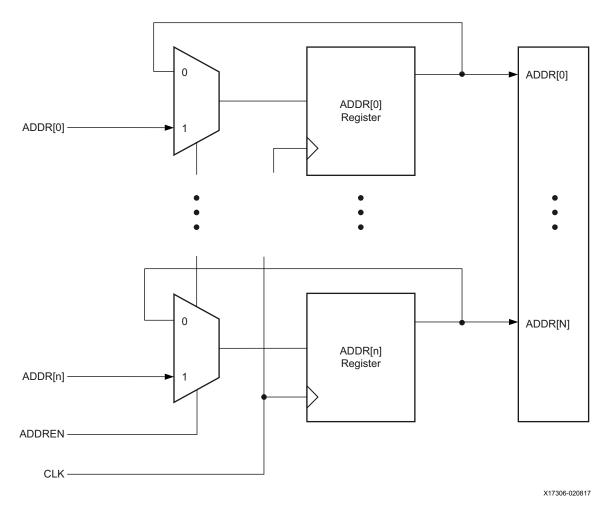

#### **Address Enable**

This feature allows the new address to be captured only when address EN is High. If the address EN is Low, the old address remains internally latched and is used for internal access. Any change in address input is ignored. This feature is controlled by the ENADDREN attribute. See Figure 1-12.

Figure 1-12: Address Latching Enable

# **Byte-Wide Write Enable**

The byte-wide write enable feature of the block RAM enables the writing of eight-bit (one byte) portions of incoming data. There are four independent byte-wide write enable inputs to the RAMB36E2 true dual-port RAM. In TDP mode for RAMB36E2, there are two ports, A and B, each of which have a 4-bit write enable bus (one bit corresponding to each data byte). In SDP mode for RAMB36E2, there is one write port, which has an 8-bit write enable bus (one bit corresponding to each data byte). Table 1-6 summarizes the byte-wide write enables for the 36 Kb and 18 Kb block RAM. Each byte-wide write enable is associated with one byte of input data and one parity bit. The byte-wide write enable inputs must be driven in accordance with the data width configurations. This feature is useful when using block RAM to interface with a microprocessor. Byte-wide write enable is not available in the ECC mode. Byte-wide write enable is further described in Additional RAMB18E2 and RAMB36E2 Primitive Design Considerations, page 48. Figure 1-13 shows the byte-wide write enable timing diagram for the RAMB36E2.

Figure 1-13: Byte-wide Write Operation Waveforms (x36 WRITE\_FIRST)

**Table 1-6:** Available Byte-Wide Write Enables

| Primitive          | Maximum Bit<br>Width | Number of Byte-Wide<br>Write Enables |

|--------------------|----------------------|--------------------------------------|

| RAMB36E2 TDP usage | 36                   | 4                                    |

| RAMB36E2 SDP usage | 72                   | 8                                    |

| RAMB18E2 TDP usage | 18                   | 2                                    |

| RAMB18E2 SDP usage | 36                   | 4                                    |

When the RAMB36E2 is configured for a 36-bit or 18-bit wide datapath, any port can restrict writing to specified byte locations within the data word. If configured in READ\_FIRST mode, the DOUT bus shows the previous content of the whole addressed word. In WRITE\_FIRST mode, DOUT shows a combination of the newly written enabled byte(s), and the initial memory contents of the unwritten bytes.

#### **Block RAM Error Correction Code**

Both block RAM and FIFO implementations of the 36 Kb block RAM support a 64-bit ECC implementation. The code is used to detect single- and double-bit errors in block RAM data read out. Single-bit errors are then corrected in the output data.

## **Power Gating of Unused Block RAMs**

UltraScale architecture-based devices power down unused/uninstantiated block RAM blocks at an 18 Kb granularity. Power gating is enabled on every 18 Kb block that is not instantiated in the design to save power. Power-gated 18 Kb blocks are not initialized during configuration and retain their house keeping value of zero. A valid bitstream is required for configuration and readback. Blank bitstreams are not allowed. The access to uninstantiated block RAM is prevented by disabling the internal operation.

# **Block RAM Library Primitives**

The block RAM library primitives, RAMB18E2 and RAMB36E2, are the basic building blocks for all block RAM configurations. Other block RAM primitives and macros are based on these primitives. Some block RAM attributes can only be configured using one of these primitives (e.g., pipeline register, cascade).

The input and output data buses are represented by two buses for 9-bit width (8 + 1), 18-bit width (16 + 2), and 36-bit width (32 + 4) configurations. The ninth bit associated with each byte can store parity/error correction bits or serve as additional data bits. No specific function is performed on the ninth bit. The separate bus for parity bits facilitates some designs. However, other designs safely use a 9-bit, 18-bit, or 36-bit bus by merging the regular data bus with the parity bus. Read/write and storage operations are identical for all bits, including the parity bits.

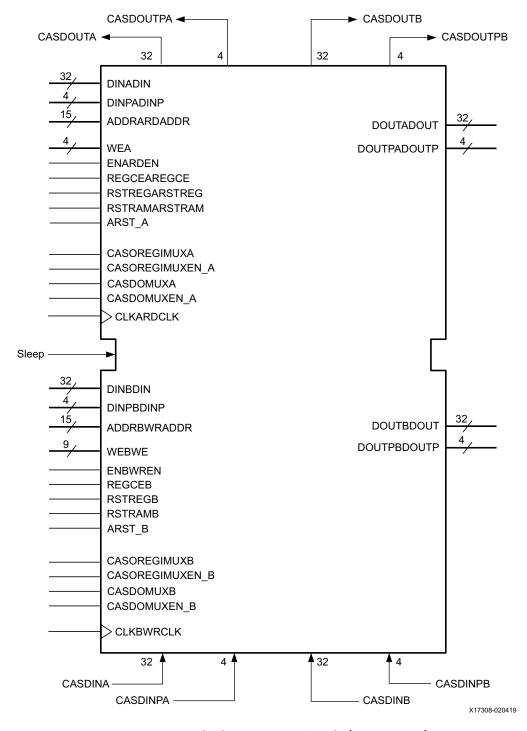

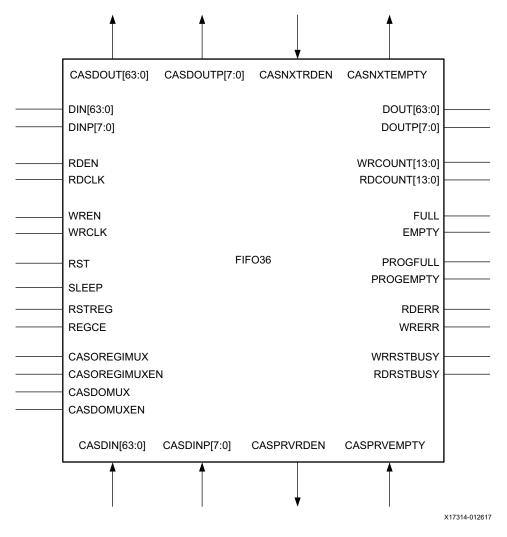

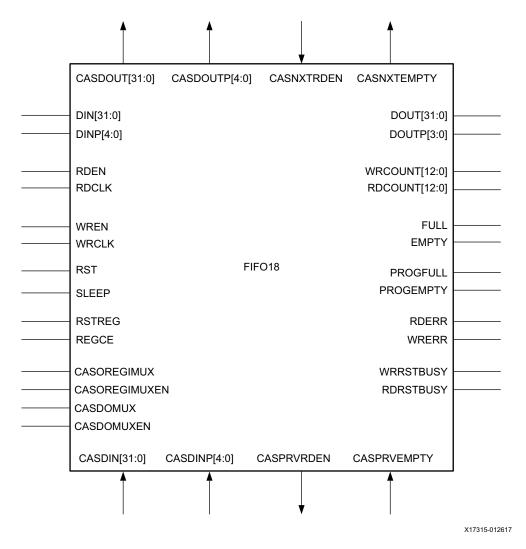

Figure 1-14 illustrates all the I/O ports of the 36 Kb true dual-port block RAM primitive (RAMB36). Table 1-7 lists these primitives.

Note: ECC pins are not shown in Figure 1-14. For more information, see Built-in Error Correction.

Figure 1-14: Block RAM Port Signals (RAMB36E2)

Table 1-7: Block RAM and FIFO Primitives

| Primitive | Description                                                                                                                                                                                                                              |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAMB36E2  | When used as TDP memory, RAMB36E2 supports port widths of x1, x2, x4, x9, x18, and x36.                                                                                                                                                  |

|           | <ul> <li>When used as SDP memory, the read or write port width is x64 or x72.</li> <li>Alternate port widths are x1, x2, x4, x9, x18, x36, and x72. In ECC mode,</li> <li>RAMB36E2 supports 64-bit ECC encoding and decoding.</li> </ul> |

| RAMB18E2  | When used as TDP memory, RAMB18E2 supports port widths of x1, x2, x4, x9, and x18.                                                                                                                                                       |

|           | • When used as SDP memory, the read or write port width is x32 or x36. Alternate port widths are x1, x2, x4, x9, x18, and x36.                                                                                                           |

| FIFO36E2  | FIFO36E2 supports port widths of x4, x9, x18, x36, and x72 for either port. When the port width is x72, ECC is optionally supported.                                                                                                     |

| FIFO18E2  | The FIFO18E2 supports port widths of x4, x9, x18, and x36 for either port.                                                                                                                                                               |

Table 1-8 shows the port names and descriptions of the primitives outlined in Table 1-7. The ECC ports are described in Built-in Error Correction.

Table 1-8: RAMB36E2 and RAMB18E2 Port Names and Descriptions

| Port Name          | Description                                                                                                                                                                   |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DINADIN[31:0]      | Port A data inputs addressed by ADDRARDADDR. See Table 1-13, page 34 for SDP usage port name mapping.                                                                         |

| DINPADINP[3:0]     | Port A data parity inputs addressed by ADDRARDADDR. See Table 1-13, page 34 for SDP usage port name mapping.                                                                  |

| DINBDIN[31:0]      | Port B data inputs addressed by ADDRBWRADDR. See Table 1-13, page 34 for SDP usage port name mapping.                                                                         |

| DINPBDINP[3:0]     | Port A data parity inputs addressed by ADDRBWRADDR. See Table 1-13, page 34 for SDP usage port name mapping.                                                                  |

| ADDRARDADDR [14:0] | Port A address input bus. When used as SDP memory, this is the RDADDR bus.                                                                                                    |

| ADDRBWRADDR[14:0]  | Port B address input bus. When used as SDP memory, this is the WRADDR bus.                                                                                                    |

| ADDRENA            | ADDRENA enables or disables the capture of a new address on port A. When disabled (Low) the old, latched address is used.                                                     |

| ADDRENB            | ADDRENB enables or disables the capture of a new address on port B. When disabled (Low) the old, latched address is used.                                                     |

| WEA[3:0]           | Port A byte-wide write enable. When used as SDP memory, this port is not used.                                                                                                |

| WEBWE[7:0]         | Port B byte-wide write enable. In SDP mode, this is the byte-wide write enable.                                                                                               |

| ENARDEN            | Port A enable. When used as SDP memory, this is RDEN.                                                                                                                         |

| ENBWREN            | Port B enable. When used as SDP memory, this is WREN.                                                                                                                         |

| RSTREGARSTREG      | Synchronous output register set/reset as initialized by SRVAL_A (DOA_REG = 1). RSTREG_PRIORITY_A determines the priority over REGCE. When used as SDP memory, this is RSTREG. |

| RSTREGB            | Synchronous output register set/reset as initialized by SRVAL_B (DOA_REG = 1). RSTREG_PRIORITY_B determines the priority over REGCE.                                          |

Table 1-8: RAMB36E2 and RAMB18E2 Port Names and Descriptions (Cont'd)

| Port Name       | Description                                                                                                                             |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| RSTRAMARSTRAM   | Synchronous output latch set/reset as initialized by SRVAL_A (DOB_REG = 0). When used as SDP memory, this is RSTRAM.                    |

| RSTRAMB         | Synchronous output latch set/reset as initialized by SRVAL_B (DOB_REG = 0).                                                             |

| CLKARDCLK       | Port A clock input. When used as SDP memory, this is RDCLK.                                                                             |

| CLKBWRCLK       | Port B clock input. When used as SDP memory, this is WRCLK.                                                                             |

| REGCEAREGCE     | Port A output register clock enable (DOA_REG = 1). When used as SDP memory, this is REGCE.                                              |

| REGCEB          | Port B output register clock enable (DOB_REG = 1).                                                                                      |

| CASDINA[31:0]   | Port A cascade data input connected to data output of lower block RAM. For RAMB18E2: CASDINA[15:0].                                     |

| CASDINPA[3:0]   | Port A cascade parity data input connected to parity data output of lower block RAM. For RAMB18E2: CASDINPA[1:0].                       |

| CASDINB[31:0]   | Port B cascade data input connected to data output of lower block RAM. For RAMB18E2: CASDINB[15:0].                                     |

| CASDINPB[3:0]   | Port B cascade parity data input connected to parity data output of lower block RAM. For RAMB18E2: CASDINPB[1:0].                       |

| CASDOUTA[31:0]  | Port A cascade data output connected to CASDINA[31:0] of upper block RAM. For RAMB18E2: CASDOUTA[15:0].                                 |

| CASDOUTPA[3:0]  | Port A cascade parity data output connected to CASDINPA[3:0] of upper block RAM. For RAMB18E2: CASDOUTPA[1:0].                          |

| CASDOUTB[31:0]  | Port B cascade data output connected to CASDINB[31:0] of upper block RAM. For RAMB18E2: CASDOUTB[15:0].                                 |

| CASDOUTPB[3:0]  | Port B cascade parity data output connected to CASDINPB[3:0] of upper block RAM. For RAMB18E2: CASDOUTPB[1:0].                          |

| CASDOMUXA       | Selects input to control the data cascade output multiplexer for port A.                                                                |

| CASDOMUXEN_A    | Enables control for the CASDOMUXA register.                                                                                             |

| CASDOMUXB       | Selects input to control the data cascade output multiplexer for port B.                                                                |

| CASDOMUXEN_B    | Enables control for the CASDOMUXB register. When used as SDP memory, this port is not used.                                             |

| CASOREGIMUXA    | Selects input to control the cascade multiplexer before the output register for Port A.                                                 |

| CASOREGIMUXEN_A | Enables control for the CASOREGIMUXA register.                                                                                          |

| CASOREGIMUXB    | Selects input to control the cascade multiplexer before the output register for Port B. When used as SDP memory, this port is not used. |

| CASOREGIMUXEN_B | Enables control for the CASOREGIMUXB register. When used as SDP memory, this port is not used.                                          |

| CASDIMUXA       | Selects input to control the cascade DIN multiplexer for Port A.                                                                        |

| CASDIMUXB       | Selects input to control the cascade DIN multiplexer for Port B. When used as SDP memory, this port is not used.                        |

Table 1-8: RAMB36E2 and RAMB18E2 Port Names and Descriptions (Cont'd)

| Port Name        | Description                                                                                                                             |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| DOUTADOUT[31:0]  | Port A data output bus addressed by ADDRARDADDR. See Table 1-13, page 34 for SDP usage port name mapping. RAMB18E2: DOUTADOUT[15:0].    |

| DOUTPADOUTP[3:0] | Port A parity output bus addressed by ADDRARDADDR. See Table 1-13, page 34 for SDP usage port name mapping. RAMB18E2: DOUTPADOUTP[1:0]. |

| DOUTBDOUT[31:0]  | Port B data output bus addressed by ADDRBWRADDR. See Table 1-13, page 34 for SDP usage port name mapping. RAMB18E2: DOUTBDOUT[15:0].    |

| DOUTPBDOUTP[3:0] | Port B parity output bus addressed by ADDRBWRADDR. See Table 1-13, page 34 for SDP usage port name mapping. RAMB18E2: DOUTPBDOUTP[1:0]. |

| SLEEP            | Dynamic power gating.                                                                                                                   |

# **Block RAM Port Signals**

Each block RAM port operates independently of the other while accessing the same set of 36 Kbit memory cells.

#### Clock – CLKARDCLK and CLKBWRCLK

Each port is fully synchronous with independent clock pins. All port input pins have setup time referenced to the port CLK pin. The output data bus has a clock-to-out time referenced to the CLK pin. Clock polarity is configurable (rising edge by default). When used as SDP memory, the CLKA port is the RDCLK and the CLKB port is the WRCLK.

#### Enable – ENARDEN and ENBWREN

The enable pin affects the read, write, and set/reset functionality of the port. Ports with an inactive enable pin keep the output pins in the previous state and do not write data to the memory cells. Enable polarity is configurable (active-High by default). When used as SDP memory, the ENA port is the RDEN and the ENB port is the WREN.

# Byte-Wide Write Enable – WEA and WEBWE

To write the content of the data input bus into the addressed memory location, both EN and WE must be active within a setup time before the active clock edge. The output latches are loaded or not loaded according to the write configuration (WRITE\_FIRST, READ\_FIRST, NO\_CHANGE). When WE is inactive and EN is active, a read operation occurs, and the contents of the memory cells referenced by the address bus appear on the data-out bus, regardless of the write mode attribute. Write enable polarity is not configurable (active-High). When used as SDP memory, the WEBWE[7:0] port is the byte-write enable. When used as TDP memory, the WEA[3:0] and WEB[3:0] are byte-write enables for port A and port B, respectively. See also Byte-Wide Write Enable, page 49.

# Register Enable – REGCEAREGCE and REGCEB

The register enable pin (REGCE) controls the optional output register. When the block RAM is in register mode, REGCE = 1 registers the output into a register at a clock edge. The polarity of REGCE is not configurable (active-High). When used as SDP memory, the REGCEA port is the REGCE.

# Set/Reset

#### RSTREGARSTREG, RSTREGB, RSTRAMARSTRAM, and RSTRAMB

In latch mode, the RSTRAM pin synchronously forces the data output latches to contain the value SRVAL. When the optional output registers are enabled (DO\_REG = 1), the RSTREG signal synchronously forces the data output registers containing the SRVAL value. The priority of RSTREG over REGCE is determined using the RSTREG\_PRIORITY attribute. The data output latches or output registers are synchronously asserted to 0 or 1, including the parity bit. Each port has an independent SRVAL[A|B] attribute of 36 bits. This operation does not affect RAM memory cells and does not disturb write operations on the other port. The polarity for both signals is configurable (active-High by default). When used as SDP memory, the RSTREGA port is the RSTREG, and the RSTRAMA port is the RSTRAM.

#### Address Bus – ADDRARDADDR and ADDRBWRADDR

The address bus selects the memory cells for read or write. When used as SDP memory, the ADDRA port is the RDADDR and the ADDRB port is the WRADDR. The data bit width of the port determines the required address bus width for a single RAMB18E2 or RAMB36E2, as shown in Table 1-9, Table 1-10, Table 1-11, and Table 1-12.

| Port Data<br>Width | Port Address<br>Width | Depth  | ADDR Bus | DIN Bus<br>DOUT Bus | DINP Bus<br>DOUTP Bus |

|--------------------|-----------------------|--------|----------|---------------------|-----------------------|

| 1                  | 14                    | 16,384 | [13:0]   | [0]                 | NA                    |

| 2                  | 13                    | 8,192  | [13:1]   | [1:0]               | NA                    |

| 4                  | 12                    | 4,096  | [13:2]   | [3:0]               | NA                    |

| 9                  | 11                    | 2,048  | [13:3]   | [7:0]               | [0]                   |

| 18                 | 10                    | 1,024  | [13:4]   | [15:0]              | [1:0]                 |

Table 1-10: Port Aspect Ratio for RAMB18E2 (When Used as SDP Memory)

| Port Data<br>Width <sup>(1)</sup> | Alternate Port<br>Width | Port Address<br>Width | Depth  | ADDR Bus | DIN Bus<br>DOUT Bus | DINP Bus<br>DOUTP Bus |

|-----------------------------------|-------------------------|-----------------------|--------|----------|---------------------|-----------------------|

| 32                                | 1                       | 14                    | 16,384 | [13:0]   | [0]                 | NA                    |

| 32                                | 2                       | 13                    | 8,192  | [13:1]   | [1:0]               | NA                    |

| 32                                | 4                       | 12                    | 4,096  | [13:2]   | [3:0]               | NA                    |

| 36                                | 9                       | 11                    | 2,048  | [13:3]   | [7:0]               | [0]                   |

| 36                                | 18                      | 10                    | 1,024  | [13:4]   | [15:0]              | [1:0]                 |

| 36                                | 36                      | 9                     | 512    | [13:5]   | [31:0]              | [3:0]                 |

#### Notes:

Table 1-11: Port Aspect Ratio for RAMB36E2 (When Used as TDP Memory)

| Port Data<br>Width | Port Address<br>Width | Depth  | ADDR Bus | DIN Bus<br>DOUT Bus | DINP Bus<br>DOUTP Bus |

|--------------------|-----------------------|--------|----------|---------------------|-----------------------|

| 1                  | 15                    | 32,768 | [14:0]   | [0]                 | NA                    |

| 2                  | 14                    | 16,384 | [14:1]   | [1:0]               | NA                    |

| 4                  | 13                    | 8,192  | [14:2]   | [3:0]               | NA                    |

| 9                  | 12                    | 4,096  | [14:3]   | [7:0]               | [0]                   |

| 18                 | 11                    | 2,048  | [14:4]   | [15:0]              | [1:0]                 |

| 36                 | 10                    | 1,024  | [14:5]   | [31:0]              | [3:0]                 |

| 1 (Cascade)        | 16                    | 65,536 | [15:0]   | [0]                 | NA                    |

Table 1-12: Port Aspect Ratio for RAMB36E2 (When Used as SDP Memory)

| Port Data<br>Width <sup>(1)</sup> | Alternate Port<br>Width | Port Address<br>Width | Depth  | ADDR<br>Bus | DIN Bus<br>DOUT Bus | DINP Bus<br>DOUTP Bus |

|-----------------------------------|-------------------------|-----------------------|--------|-------------|---------------------|-----------------------|

| 64                                | 1                       | 15                    | 32,768 | [14:0]      | [0]                 | NA                    |

| 64                                | 2                       | 14                    | 16,384 | [14:1]      | [1:0]               | NA                    |

| 64                                | 4                       | 13                    | 8,192  | [14:2]      | [3:0]               | NA                    |

| 72                                | 9                       | 12                    | 4,096  | [14:3]      | [7:0]               | [0]                   |

| 72                                | 18                      | 11                    | 2,048  | [14:4]      | [15:0]              | [1:0]                 |

| 72                                | 36                      | 10                    | 1,024  | [14:5]      | [31:0]              | [3:0]                 |

| 72                                | 72                      | 9                     | 512    | [14:6]      | [63:0]              | [7:0]                 |

#### Notes:

1. Either the read or write port is a fixed width of x64 or x72.

<sup>1.</sup> Either the read or write port is a fixed width of x32 or x36.

For block RAMs used as SDP memories, the port name mapping is listed in Table 1-13. Figure 1-6 shows the SDP data flow.

Table 1-13: Port Name Mapping for Block RAMs Used as SDP Memories

| RAMB18E2 Used                    | l as SDP Memory                  | RAMB36E2 Used as SDP Memory      |                                  |  |

|----------------------------------|----------------------------------|----------------------------------|----------------------------------|--|

| X36 Mode (Width = 36)            | X18 Mode (Width ≤ 18)            | X72 Mode (Width = 72)            | X36 Mode (Width ≤ 36)            |  |

| DIN[15:0] =<br>DINADIN[15:0]     | DIN[15:0] =<br>DINBDIN[15:0]     | DIN[31:0] =<br>DINADIN[31:0]     | DIN[31:0] =<br>DINBDIN[31:0]     |  |

| DINP[1:0] =<br>DINPADIN[1:0]     | DINP[1:0] =<br>DINPBDINP[1:0]    | DINP[3:0] =<br>DINPADIN[3:0]     | DINP[3:0] =<br>DINPBDINP[3:0]    |  |

| DIN[31:16] =<br>DINBDIN[15:0]    |                                  | DIN[63:32] =<br>DINBDIN[31:0]    |                                  |  |

| DINP[3:2] =<br>DINPBDINP[1:0]    |                                  | DINP[7:4] =<br>DINPBDINP[3:0]    |                                  |  |

| DOUT[15:0] =<br>DOUTADOUT[15:0]  | DOUT[15:0] =<br>DOUTADOUT[15:0]  | DOUT[31:0] =<br>DOUTADOUT[31:0]  | DOUT[31:0] =<br>DOUTADOUT[31:0]  |  |

| DOUTP[1:0] =<br>DOUTPADOUTP[1:0] | DOUTP[1:0] =<br>DOUTPADOUTP[1:0] | DOUTP[3:0] =<br>DOUTPADOUTP[3:0] | DOUTP[3:0] =<br>DOUTPADOUTP[3:0] |  |

| DOUT[31:16] =<br>DOUTBDOUT[15:0] |                                  | DOUT[63:32] =<br>DOUTBDOUT[31:0] |                                  |  |

| DOUTP[3:2] =<br>DOUTPBDOUTP[1:0] |                                  | DOUTP[7:4] =<br>DOUTPBDOUTP[3:0] |                                  |  |

# Data-In Buses – DINADIN, DINPADINP, DINBDIN, and DINPBDINP

Data-in buses provide the new data value to be written into RAM. The regular data-in bus (DIN), plus the data-in parity bus (DINP), when available, have a total width equal to the port width. For example, the 36-bit port data width is represented by DIN[31:0] and DINP[3:0], as shown in Table 1-9, page 32 through Table 1-12. See Table 1-13 for port name mapping for block RAMs used as SDP memories.

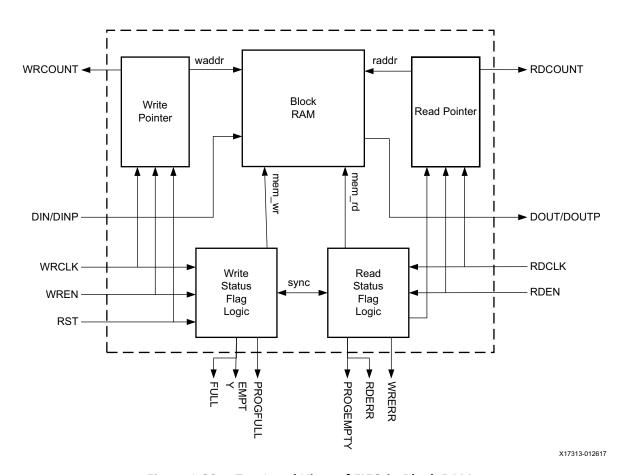

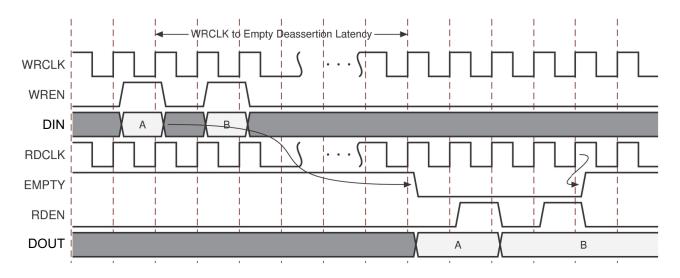

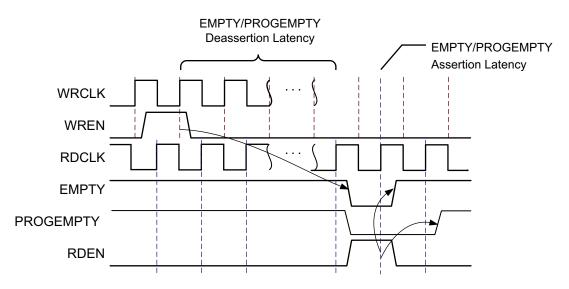

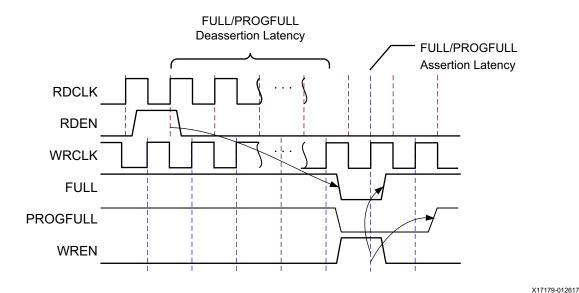

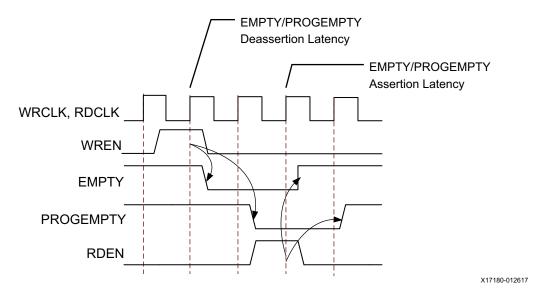

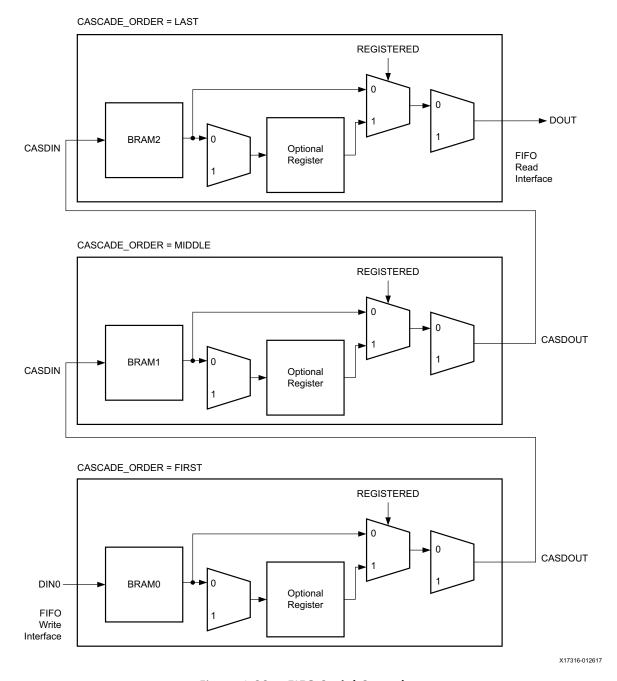

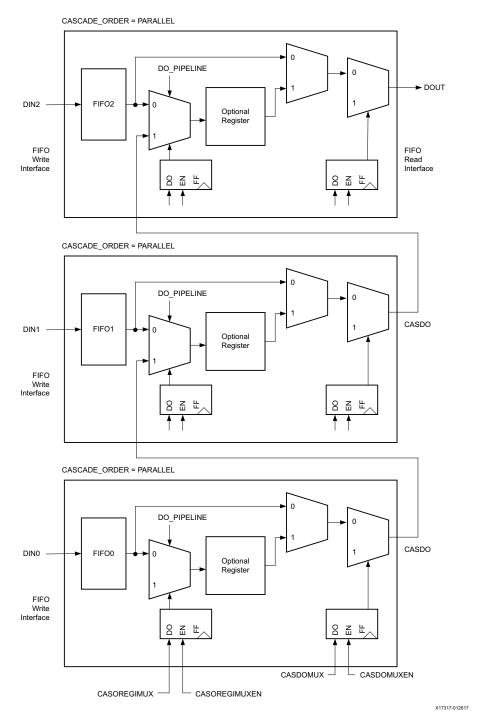

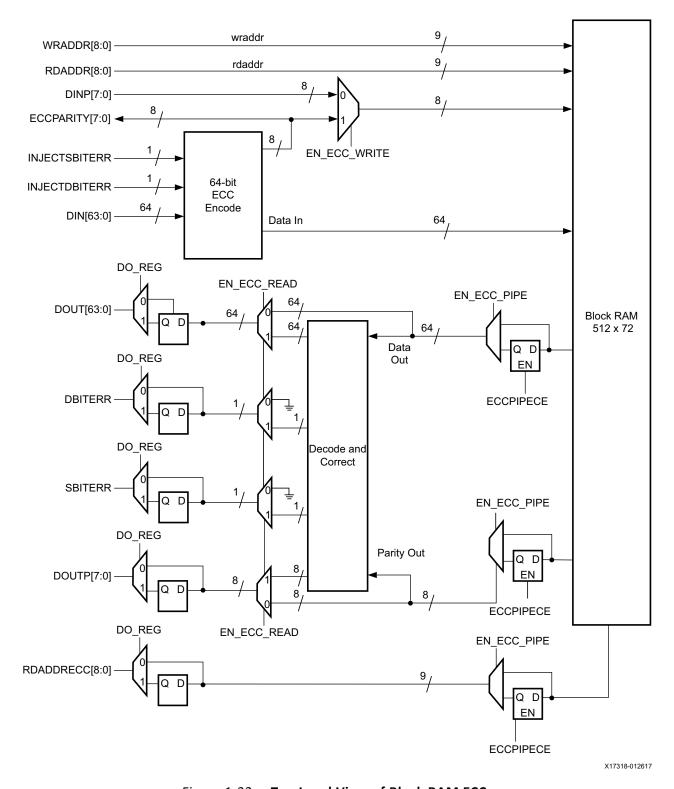

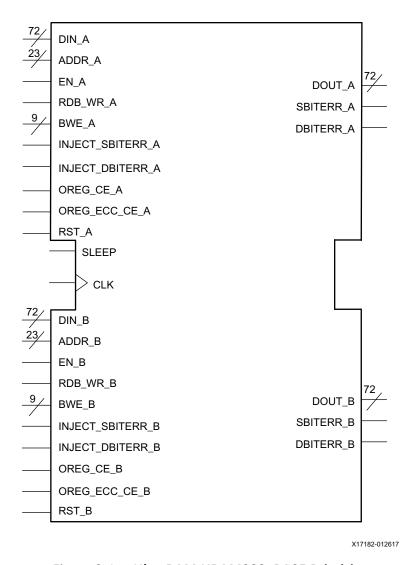

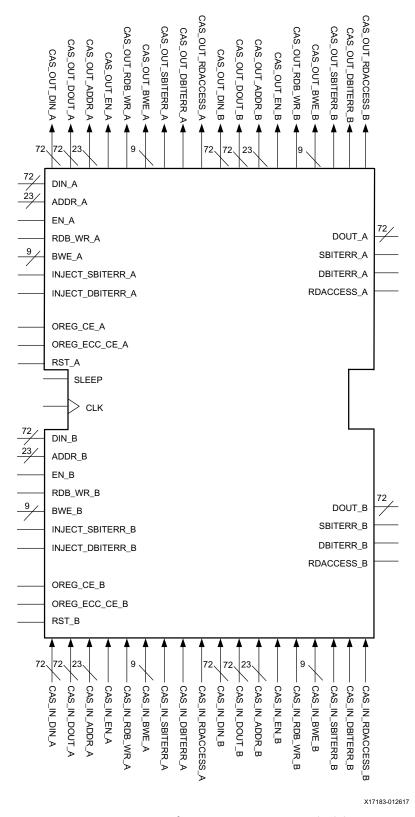

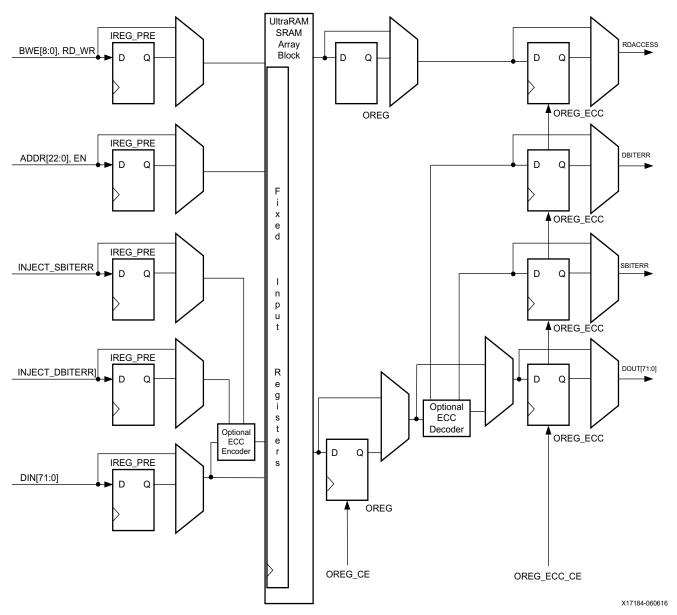

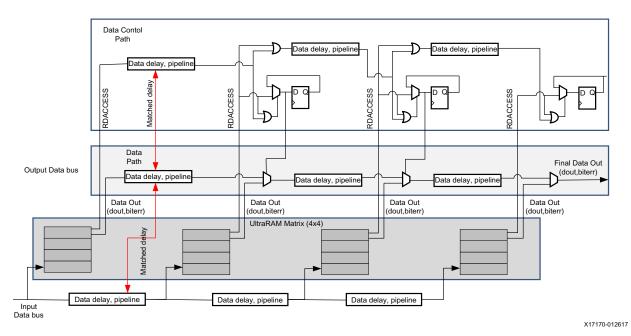

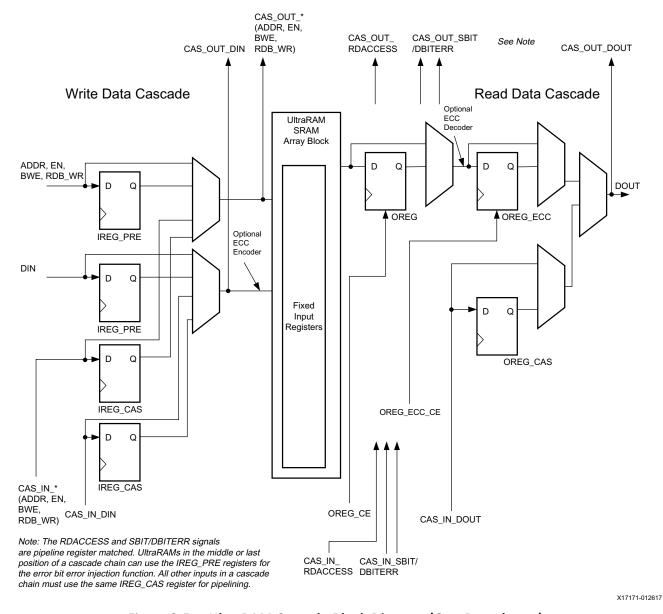

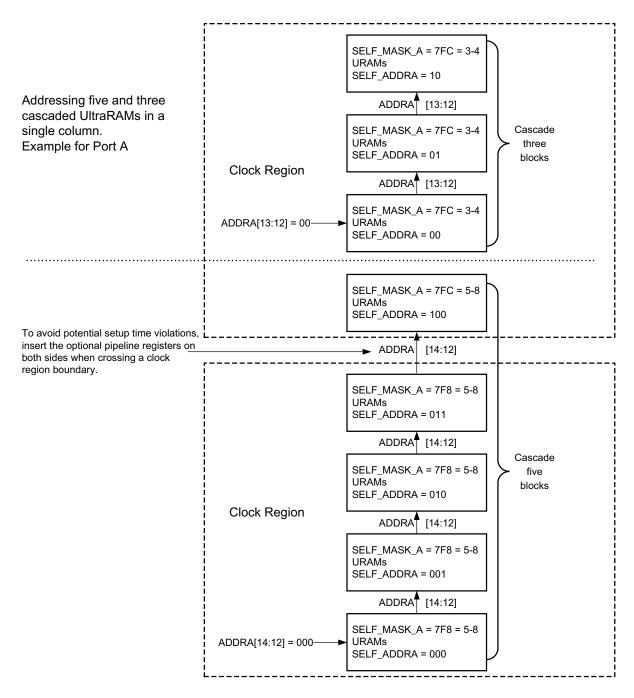

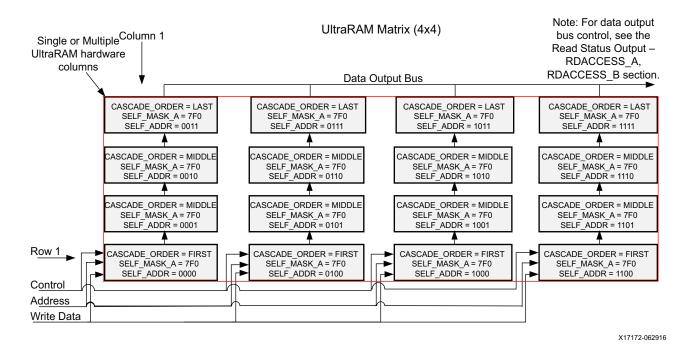

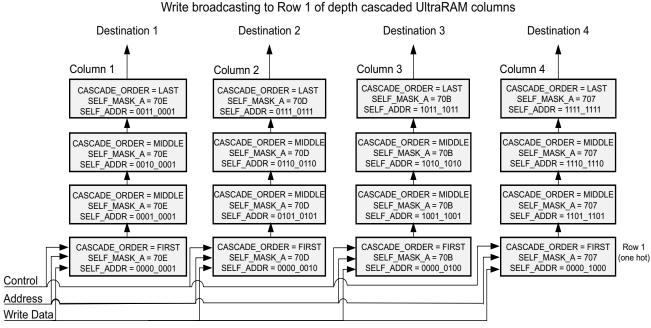

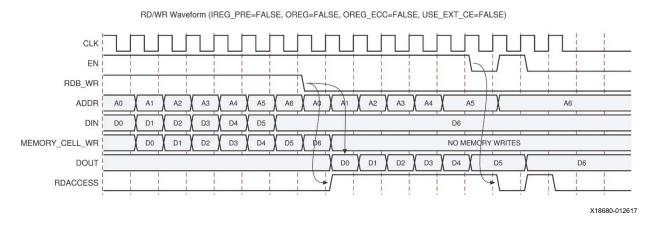

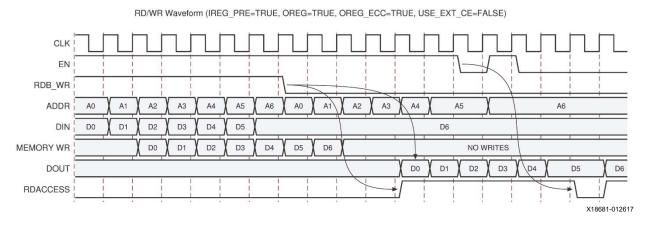

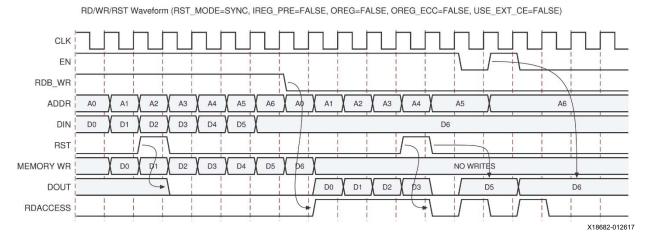

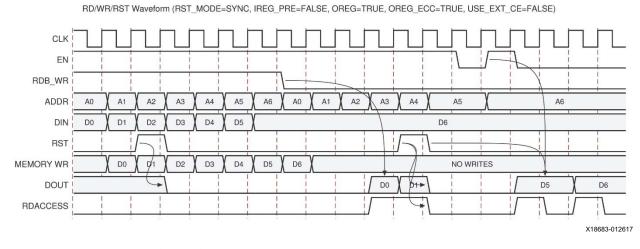

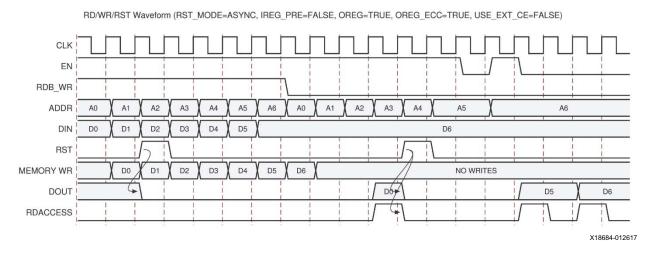

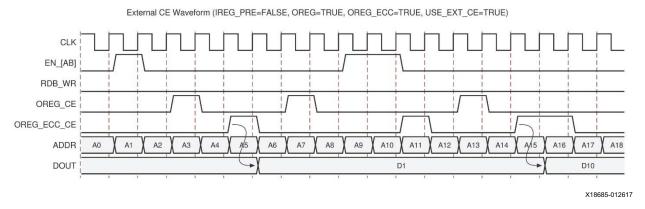

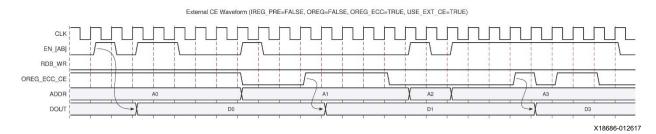

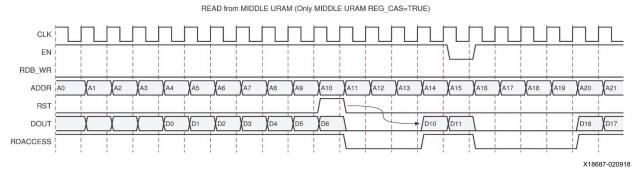

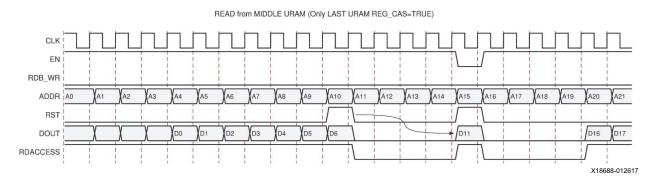

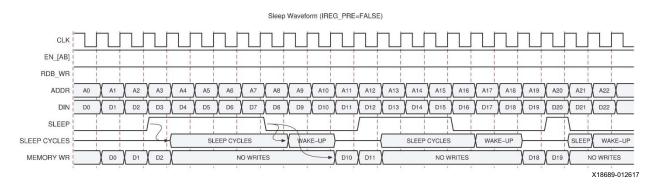

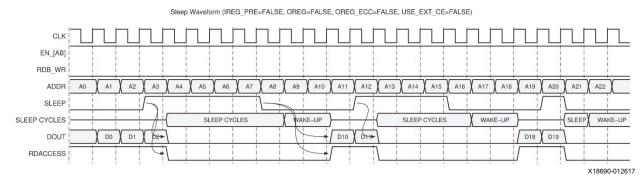

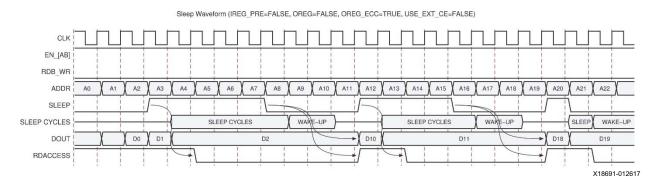

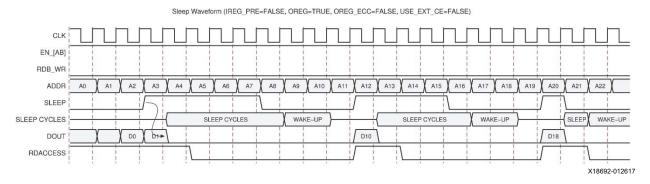

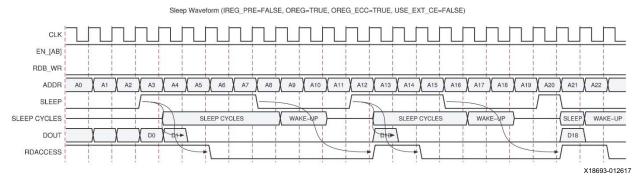

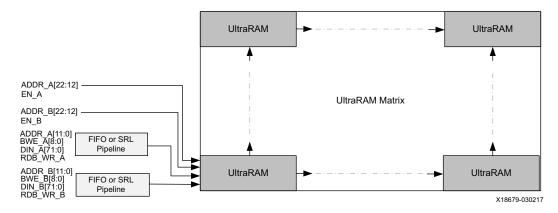

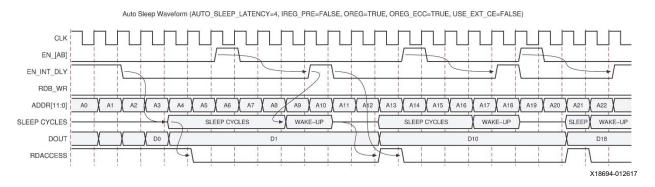

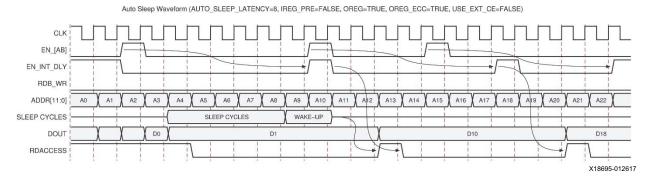

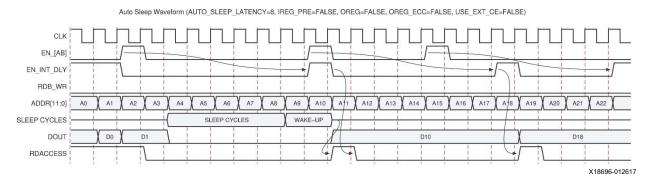

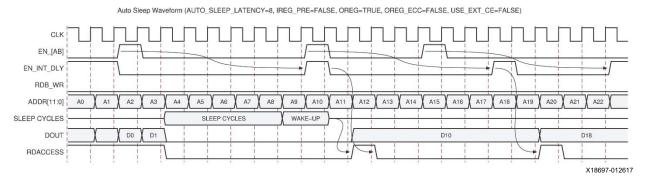

# Data-Out Buses – DOUTADOUT, DOUTPADOUTP, DOUTBDOUT, and DOUTPBDOUTP