Design and implementation of an UDP/IP Ethernet hardware protocol stack for FPGA based Systems

A Master's Thesis

Submitted to the Faculty of the

Escola Tècnica d'Enginyeria de Telecomunicació de

Barcelona

Universitat Politècnica de Catalunya

by

Gerard Guixé Orriols

In partial fulfilment

of the requirements for the degree of

MASTER IN ELECTRONIC ENGINEERING

**Advisor: Francesc Moll Echeto**

Barcelona, January 2019

<u>Title of the thesis:</u> Design and implementation of an UDP/IP Ethernet hardware protocol stack for FPGA based Systems

**Author:** Gerard Guixé Orriols

**Advisor:** Francesc Moll Echeto

## **Abstract**

The main objective of the thesis has been the design and implementation of a complete UDP/IP Ethernet stack that allow us the connection and use of networks by any FPGA device. The stack has been designed around Ethernet, IPv4 and UDP protocols as it was wanted a fast and scalable way of distant communication. Other protocols have been added as a complement in order to improve its operation like ARP and DHCP.

The project has focused around the implementation of this stack as a generic IP core, but it has been extended further on with the implementation of an initial data acquisition interface (DAQ) that would allow us to transmit the information of its channels to the network. At the end, the project has been successfully implemented in a real FPGA system. And all the tests have been passed with minimum packet loss, from simple operational test to more final ones like the test of a DAQ service interface.

# **Acknowledgements**

I want to give thanks to both my directors Joan Mauricio Ferré and Francesc Moll Echeto, for his support during the project and all the advice given through the work. Also, thanks to all the people in the ICCUB for giving me the tools and help that was needed to develop this project and for the plentiful coffee breaks.

Thank you too, to all my friends Ana, Anna, Carlos, David, Didac, Guillem, Hasari, Hochi, Jordi, Judit, Nerea, Patricia, Quique, Sofia, Thais and Tom for being there and make of me a less productive person when it was really necessary.

And of course, many thanks to my parents and family for their support and understanding, and for rising me with a love for technology, and lots of 80s sci-fi.

# Revision history and approval record

| Revision | Date       | Purpose           |

|----------|------------|-------------------|

| 0        | 30/10/2018 | Document creation |

| 1        | 14/12/2018 | Document revision |

| 2        | 27/12/2018 | Document revision |

|          |            |                   |

| Written by: |                | Reviewed and approved by: |                    |  |  |  |  |  |

|-------------|----------------|---------------------------|--------------------|--|--|--|--|--|

| Date        | 30/10/2018     | Date                      | 27/12/2018         |  |  |  |  |  |

| Name        | Gerard Guixé   | Name                      | Francesc Moll      |  |  |  |  |  |

| Position    | Project Author | Position                  | Project Supervisor |  |  |  |  |  |

# **Table of contents**

| Abstract                                                   | 2  |

|------------------------------------------------------------|----|

| Acknowledgements                                           | 3  |

| Revision history and approval record                       | 4  |

| Table of contents                                          | 5  |

| List of Figures                                            | 8  |

| List of Tables                                             | 10 |

| 1. Introduction                                            | 11 |

| 1.1. Objectives                                            | 11 |

| 1.2. Work plan                                             | 11 |

| 2. State of the art of the Internet Protocol               | 14 |

| 2.1. The Internet protocol suite                           | 14 |

| 2.1.1. The OSI model                                       | 15 |

| 2.2. Physical layer                                        | 17 |

| 2.2.1. Media-independent interface (MII)                   | 17 |

| 2.2.2. Reduced gigabit media-independent interface (RGMII) | 18 |

| 2.3. Data link layer                                       | 19 |

| 2.3.1. Ethernet protocol                                   | 19 |

| 2.3.1.1. MAC addresses                                     | 20 |

| 2.3.1.2. Ethernet frame                                    | 20 |

| 2.3.2. Address Resolution Protocol (ARP)                   | 22 |

| 2.3.2.1. ARP cache                                         | 22 |

| 2.4. Network layer                                         | 23 |

| 2.4.1. Internet protocol version 4 (IPv4)                  | 23 |

| 2.4.1.1. Protocol header                                   | 23 |

| 2.4.1.2. Fragmentation                                     | 25 |

| 2.4.1.3. Protocol addresses                                | 25 |

| 2.4.2. Internet Control Message Protocol (ICMP)            | 26 |

| 2.5. Transport layer                                       | 27 |

| 2.5.1. User Datagram Protocol (UDP)                        | 28 |

| 2.5.1.1. Protocol Header                                   | 28 |

| 2.5.1.2. Ports                                             | 28 |

| 2.5.1.3. Checksum computation                              | 29 |

|    | 2.5   | .2.    | Transmission Control Protocol (TCP)        | .29 |

|----|-------|--------|--------------------------------------------|-----|

|    | 2.6.  | Apı    | plication layer                            | .29 |

|    | 2.6   | .1.    | Dynamic Host Configuration Protocol (DHCP) | .29 |

|    | 2     | 2.6.1. | 1. DHCP header and options                 | .30 |

|    | 2.6   | .2.    | Other services                             | .32 |

|    | 2.7.  | Exi    | sting implementations                      | .32 |

| 3. | Des   | sign   | of the stack                               | .34 |

|    | 3.1.  | UD     | P/IPv4 stack core structure                | .34 |

|    | 3.2.  | RG     | MII interface                              | .37 |

|    | 3.2   | .1.    | RGMII Physical chip                        | .37 |

|    | 3.3.  | Red    | ception side (Rx)                          | .38 |

|    | 3.3   | .1.    | RGMII Rx interface                         | .38 |

|    | 3.3   | .2.    | Ethernet Rx core                           | .40 |

|    | 3.3   | .3.    | IPv4 Rx core                               | .41 |

|    | 3.3   | .4.    | UDP Rx core                                | .41 |

|    | 3.4.  | Tra    | nsmission side (Tx)                        | .42 |

|    | 3.4   | .1.    | Bus Arbiters                               | .43 |

|    | 3.4   | .2.    | RGMii Tx interface                         | .44 |

|    | 3.4   | .3.    | Ethernet Tx core                           | .45 |

|    | 3.4   | .4.    | IPv4 Tx core                               | .46 |

|    | 3.4   | .5.    | UDP Tx core                                | .47 |

|    | 3.5.  | Cei    | ntral timer                                | .47 |

|    | 3.6.  | AR     | P protocol design                          | .48 |

|    | 3.6   | .1.    | Auxiliary timers                           | .49 |

|    | 3.6   | .2.    | ARP cache design                           | .49 |

|    | 3.6   | .3.    | ARP VHDL design                            | .49 |

|    | 3.7.  | ICN    | /IP protocol design                        | .51 |

|    | 3.8.  | DH     | CP protocol design                         | .52 |

|    | 3.9.  | Des    | sign of Services                           | .53 |

|    | 3.9   | .1.    | Echo reply service                         | .53 |

|    | 3.9   | .2.    | DAQ interface service                      | .54 |

|    | 3.9   | .3.    | Adding a new service to the stack          | .55 |

|    | 3.10. | Clo    | ock constrains and timings                 | .55 |

|     | 3.10   | 0.1. Design Constrains           | 55 |

|-----|--------|----------------------------------|----|

|     | 3.10   | 0.2. Timing violations           | 56 |

| 4.  | Res    | sults                            | 57 |

| 4   | l.1.   | Hardware and Software tools      | 57 |

|     | 4.1.   | .1. FPGA board                   | 57 |

|     | 4.1.   | .2. Software tools               | 58 |

| 4   | .2.    | Timing reports                   | 59 |

| 4   | .3.    | Resource usage                   | 61 |

| 4   | .4.    | Board implementation and testing | 63 |

| 5.  | Bud    | dget                             | 69 |

| 6.  | Con    | nclusions and future development | 70 |

| 6   | 5.1.   | Conclusions                      | 70 |

| 6   | 5.2.   | Future development               | 70 |

| Bib | oliogr | raphy                            | 72 |

| Ар  | pend   | lices                            | 74 |

| Glo | ssar   | rvrv                             | 80 |

# **List of Figures**

| Figure 1. Project's Gantt Diagram                                                                                                                          | 12 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2. Network topology and data flow of the internet protocol [1]                                                                                      | 15 |

| Figure 3. Data encapsulation of the internet protocol model [1]                                                                                            | 15 |

| Figure 4. Ethernet frame with minimum and maximum number of bytes [3]                                                                                      | 20 |

| Figure 5. Format of an IPv4 header with byte references [10] [11]                                                                                          | 24 |

| Figure 6. Example of fragmentation of a Datagram [10]                                                                                                      | 25 |

| Figure 7. Format of ICMP header [15]                                                                                                                       | 26 |

| Figure 8. Standard format of UDP header [16]                                                                                                               | 28 |

| Figure 9: DHCP protocol session [18].                                                                                                                      | 30 |

| Figure 10. Block diagram of the full UDP/IPv4 stack core without timers                                                                                    | 36 |

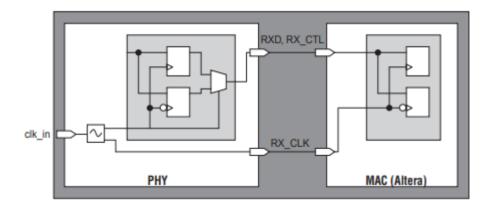

| Figure 11. Signal connections between the RGMII MAC and RGMII PHY [5]                                                                                      | 37 |

| Figure 12. Block diagram of the receive interface [5]                                                                                                      | 39 |

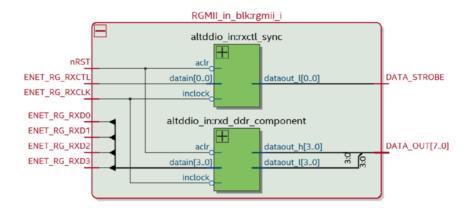

| Figure 13. RGMII physical chip generated RX_CLK signal and RXD (data), with intedelay enabled. With the internal delay both signals are center-aligned [5] |    |

| Figure 14. Final implemented design of RGMI RX core [5].                                                                                                   | 40 |

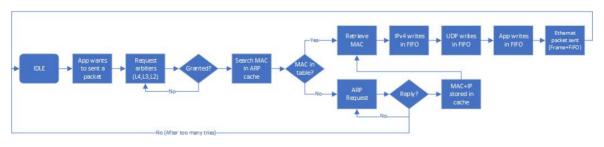

| Figure 15. Flow diagram of the transmission of a datagram using the stack                                                                                  | 42 |

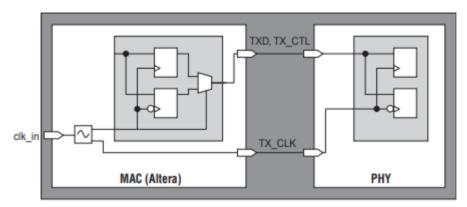

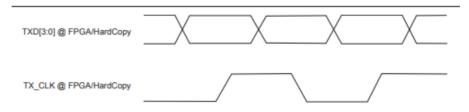

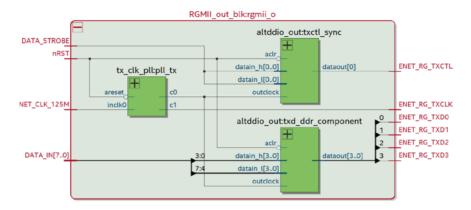

| Figure 16. Block diagram of the transmit interface [5].                                                                                                    | 44 |

| Figure 17. FPGA MAC generated signal TX_CLK with RGMII PHY internal delay disa [5].                                                                        |    |

| Figure 18. Final design of the RGMII TX block                                                                                                              | 45 |

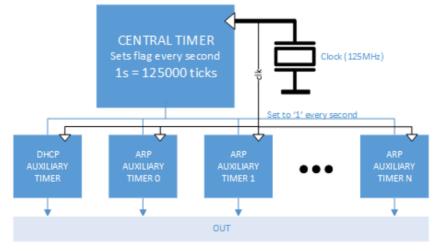

| Figure 19. Block diagram of the designed system of timers                                                                                                  | 47 |

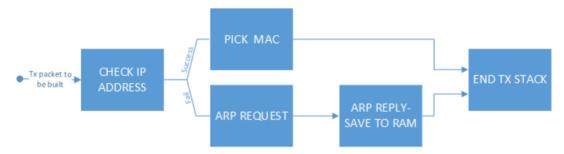

| Figure 20. Flow diagram of the ARP checking cycle when a packet has to be sent                                                                             | 48 |

| Figure 21. Block diagram of UDP/IP stack with implementation of three different servassigned to three different ports.                                     |    |

| Figure 22. Block diagram designed DAQ interface service.                                                                                                   | 54 |

| Figure 23. Intel Cyclone 10 LP FPGA Evaluation board, block diagram [30]                                                                                   | 58 |

| Figure 24. DHCP session and ping request to test acknowledgment of address                                                                                 | 63 |

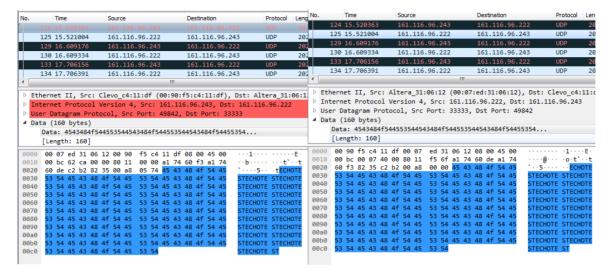

| Figure 25. Full stack test                                                                                                                                 | 64 |

| Figure 26. Echo request (left) and Echo reply (right) – The data is correctly echoed                                                                       | 65 |

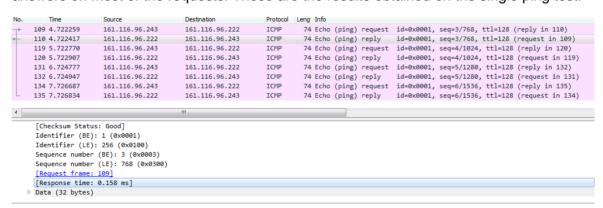

| Figure 27: Visualization of a ping to the FPGA sent from a PC, all four request have be answered                                                           |    |

| Figure 28. Windows cmd results of Ping, the packet loss is of 0%, the times haven't be                                                                     |    |

| Figure 29. Windows results of ping during 60 seconds, in this case we have some pa<br>loss (1%)                                           |    |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 30. Linux results of ping during 60 seconds, we have some packet loss (6%)                                                         | 66 |

| Figure 31. Windows and Linux simultaneous Ping for 60 seconds, result of one of the test. Packet loss of 1% for windows and 5% for Linux. |    |

| Figure 32. Multiple services working at the same time with the stack                                                                      | 67 |

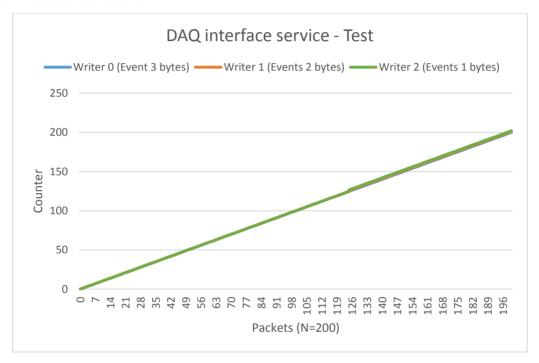

| Figure 33. Data received at the DAQ interface service test, as we can see the losses minimal                                              |    |

# **List of Tables**

| Table I. OSI Model and IP model table of equivalencies [1] [2]1                                                             |

|-----------------------------------------------------------------------------------------------------------------------------|

| Table II. RGMII Ethernet supported speeds [4]1                                                                              |

| Table III. Minimum input and output ports needed in a RGMII for a working chip [4] [5]1                                     |

| Table IV. Example of some ICMP control messages [15]2                                                                       |

| Table V. Some of the most common DHCP options, most of them used in the design of the project [20]                          |

| Table VI. List of the system arbiters and the protocols they have at the input and output4                                  |

| Table VII. FPGA Cyclone 10 hardware characteristics5                                                                        |

| Table VIII. Timing reports for model (slow, 1200mV, 85°C)6                                                                  |

| Table IX. Timing reports for model (slow, 1200mV, 0°C)6                                                                     |

| Table X. Timing reports for model (fast, 1200mV, 0°C)6                                                                      |

| Table XI. Resource usage report summary of the UDP/IP Ethernet stack6                                                       |

| Table XII. Resource usage report summary of the UDP/IP Ethernet stack with DAQ and Echo Reply services                      |

| Table XIII. Average, Median, Maximum and Minimum loss values of 50 test with Window and Linux sending pings simultaneously6 |

| Table XIV. Budget Table6                                                                                                    |

## 1. Introduction

This project has been made in collaboration with the Technological Unit of the Institute of Cosmos Sciences (ICCUB). The Unit works in a high number of electronic related projects, designing ICs and PCBs, and making full systems with very specific functions. Most of the systems have an FPGA integrated.

The project initially arose from a very specific need. The Institute works with various systems which require very fast data acquisition devices (DAQ). The systems typically consist in one or more Front-End ASICs which amplify, shape and digitize signals coming from photosensors. Then, the FPGA acquires the digital data and then sent it via USB to an external computer.

The disadvantage of this design is that there is the constant need of a computer physically connected to the board in order to gather data and if it was needed some kind of configuration to the board it can only be made using that computer. The use of USB has strict limitations in distance and scalability. There was also a need to communicate the boards to a network without adding a lot of extra components to the already existent PCBs.

Then, it was proposed the design of a communication stack that would allow the PCB designs to connect, send and receive messages through various types of networks. This design would be implemented in an FPGA, as it is an integral part of the boards. The stack would allow to communicate to any computer connected to the network, and would allow at least some kind of communication via Internet. As we were working with DAQ sending data at high speed, there was a need of a fast communication, prioritizing speed over reliability. That is when it finally showed up the final idea for this Thesis, the creation of an UDP/IP Ethernet protocol stack IP core, that would be implemented in an FPGA (Cyclone 10 LP) using some hardware description language.

Some other specifications were created after that, for example it was important that the system was easy to set, and easy to move around. For this reason, some other protocols were set as main objectives like ARP or DHCP. The project focuses specifically on the stack and a few initial services, but it has been left open the possibility of creating a greater number of different applications that would increase the uses and complexity of the project.

### 1.1. Objectives

The main objectives defined for the project are the following ones:

- Design of an UDP/IP Ethernet hardware protocol stack.

- Implementation of the design in an FPGA system with VHDL or Verilog.

- Incorporation of a dynamic host configuration protocol (DHCP) for highest adaptability in all type of networks.

- Creation of client-side applications to manage systems and data related to the FPGA via Ethernet.

#### 1.2. Work plan

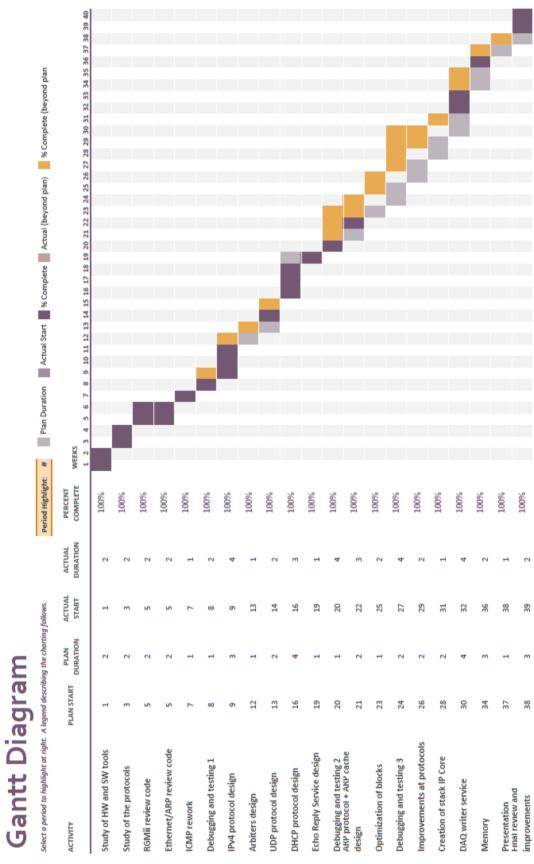

The thesis was planned as a 9-month project working between 4 and 6 hours each working day. This is the Gantt diagram of the project:

Figure 1. Project's Gantt Diagram

As we can appreciate taking a look at the Gantt, the Project was delayed from the planned dates, and the delay was kept for all the duration of the project from week 21.

The most delayed activities were the debugging and testing sections, they were planned for relatively short times like 1 or 2 weeks, but at the end they all doubled their durations. These delays appear due to a lot of unexpected problems that originate during the development of the stack, some of them were unexpected at a new challenge, so they took longer to solve.

One of the most remarkable problems was the appearance of timing violations (a negative slack in the main clock). This timing violations were a huge problem, as they induced an unpredictable behavior to the stack. In order to solve these violations, some signals were pipelined, this is further explained in Section 3.10 Timing Violations. As the violations appeared very late on the project, the latch of signals desynchronizes most of the protocols, and it made necessary a rework of timings and counters in most of the protocols.

## 2. State of the art of the Internet Protocol

The project focuses on the design of a protocol stack as digital hardware in an FPGA. This means the implementation of a protocol suite that will fit our communication needs with other devices in the network.

Studying our own needs, it was decided to implement the Internet Protocol suite. This suite has a large number of protocols that can work over all kind of networks and can communicate with all kind of devices, the use of the Internet Protocol suite, makes the communication with personal computers very easy and that was one of the main objectives.

In this section we will analyze the Internet Protocol suite as a whole, and later on we will make a review of some of the individual protocols that are part of this suite. We will make a special focus on the protocols that have been implemented in our design, and in the next sections we will talk about the justifications of these choices.

## 2.1. The Internet protocol suite

The Internet protocol suite was created as a model that group the communication protocols used in the Internet Network and in other similar network systems [1]. The main protocols used in Internet are the Internet Protocol (IP) and Transmission Control Protocol (TCP), for this reason this suite is also sometimes called TCP/IP model.

The model has four layers of organization; they are used to classify the protocols for its functionality inside the network. The four layers are:

- Application Layer: Services that create user data and transmit it to other services through a network. Process to process communication.

- Transport Layer: Host to host communication. Reliability and flow control, multiplexing, can provide control-oriented communications. Main protocols are UDP and TCP.

- Internet Layer: Transport of packets across the network. Address and route of structures. Main protocol here is IP.

- Link Layer: Protocols that operate at the physical link level.

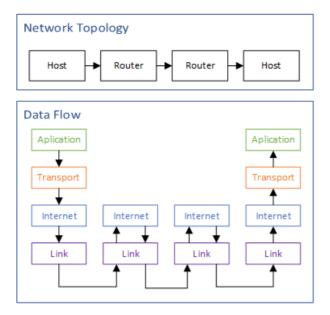

The model hides the network topology behind the protocols. Two host can communicate transmitting and receiving messages as if they were directly connected as seen in the network topology of Figure 2. Network topology and The host use the routers as a direct pipeline, all the complex processes are happening in the lower layers as seen in the Data Flow of the same figure. That flow is ignored by the host applications.

Figure 2. Network topology and data flow of the internet protocol [1]

Internet suite packets use encapsulation in each layer [1]. The data from the highest layer is encapsulated in the next one, this one at the same time is encapsulated in its next, this happens in each level of the protocol. This encapsulation process can be easily understood looking at Figure 3. Data encapsulation of the internet protocol model Data encapsulation of the internet protocol model provides abstraction to the protocols, the highest protocol sends the data down to the other layers, and it does not interact with them in any way, the data starts encapsulating until we reach the final layer and the data is transmitted. This simplify the communication and the interactions between layers.

Figure 3. Data encapsulation of the internet protocol model [1]

#### 2.1.1. The OSI model

The OSI (Open System Interconnections) model serves as way of standardization of all the telecommunication protocols without the need of knowing the technology used or the hardware structure [2].

The final goal of the model is to simplify the use and understanding of different communication systems and standard protocols. The model splits theses system and protocols in a set of specific layers. The standard model has seven layers: the physical layer, the data link layer, the network layer, the transport layer, the session layer, the

presentation layer and finally the application layer. These layers describe the different steps that a bit of data has to cover in order to be correctly manage, transmit and receive.

During the project, the model has been used to classify the protocols used in the stack and to help in explanations and diagrams. The internet protocol model was created before the OSI model. Both models are constantly compared, this leads to confusion, because both models have different objectives, and assume different things.

If we compare the OSI model with the Internet protocol suite we see that both models have layers with similarities: The TCP/IP model Application layer includes the three top layers of the OSI model (Session, Presentation and Application), the transport layer is the same in both models, the Internet layer is the same as the OSI model Network layer, finally the TCP/IP Network access layer includes both the physical and data link layers of the OSI model.

With all this information we can define the following table, we have added the protocols used for the project in the correspondent layer:

Table I. OSI Model and IP model table of equivalencies [1] [2]

| OSI model          | IP model          | Layer<br>number           | PDU               | Protocols              |  |  |  |  |  |

|--------------------|-------------------|---------------------------|-------------------|------------------------|--|--|--|--|--|

| Application layer  |                   | L7                        |                   | DHCP, DAQ,<br>Echo     |  |  |  |  |  |

| Presentation layer | Application layer | Application layer L6 Data |                   |                        |  |  |  |  |  |

| Session layer      |                   | L5                        |                   | (None)                 |  |  |  |  |  |

| Transport layer    | Transport layer   | L4                        | Datagram<br>(UDP) | UDP                    |  |  |  |  |  |

| Network layer      | Internet layer    | L3                        | Packet            | IPv4, ICMP             |  |  |  |  |  |

| Data link layer    | Network access    | L2                        | Frame             | ARP, MAC (Ethernet)    |  |  |  |  |  |

| Physical layer     | layer             | L1                        | Bit               | IEEE 802.3u<br>(RGMII) |  |  |  |  |  |

The layer number is used as an abbreviation for layer names, the PDU represents the protocol data unit used in each layer. As we can see both models have equivalencies between layers.

The protocols and systems selected for the project can usually be identified to a layer but some of them are and exception as they work in more than one layer. We call them cross-layer protocols and are represented in cursive on the table, they are considered cross-layer for the following reasons:

- ARP protocol: It maps the IP addresses (L3) to MAC addresses (L2). The Ethernet

protocol needs to know what IP address is connected to each MAC in order to being

able to correctly send a message.

- DHCP protocol: It gives an IPv4 address (L3) to every new system and device that

joins the network using UDP packets (L4). The Ethernet protocol cannot obtain an

address in its own, we are in need of the DHCP.

From now on, we are going to talk about all the protocols involved in the development of our stack. The protocols have been classified following the OSI model layering. The only exception is the Application layer, due to its simplicity the three last layers of the OSI model have been represented together in a single Application layer (like in the TCP/IP model).

## 2.2. Physical layer

The physical layer (abbreviated as PHY) refers to the circuitry required in the system to connect a link layer device (abbreviated as MAC for medium access control) to a physical medium. The physical medium can be a copper cable, optical fiber or other types of medium like RF signals.

For the design of the UDP/IP stack, we have used a media-independent interface (MII) to connect with our physical medium, an Ethernet cable. We are going to talk about the MII interfaces and some of its variants, making a special focus in the reduced media-independent interface (RGMII) used in the Project.

#### 2.2.1. Media-independent interface (MII)

The media-independent interface (MII) is a standard that was defined as a way to connect any Fast Ethernet MAC block to any Physical chip. This standard allows us to connect different types of physical devices to different types of media (twister pair, optical fiber, etc.). These connections can be made with a single chip, without the need of redesigning or replacing the hardware in the MAC side [3].

The original MII protocol transfers network data with 4 transmit data bits, 4 receive data bits and a clock of 25 MHz, and it achieves speeds of 100Mbit/s. Some variants have been developed over the years to be used with higher speeds and a lower number of signals. These new variants have been necessary to match with modern technologies that are faster and more efficient. Some of the current variants with a brief description of each one are:

- Reduced media-independent interface (RMII): Reduced the number of signals that are required to interface the physical layer to the MAC.

- Gigabit media-independent interface (GMII): This interface allows speed of 10, 100 and 1000 Mbit/s. It uses two clocks, one for 10/100 and the other for 1000 Mbit/s speeds, 8 transmit data bits and 8 receive data bits.

- Reduced gigabit media-independent interface (RGMII): A combination of the last two, it uses half the data signals than a GMII interface requires and it can achieve speeds of 10/100/1000 Mbit/s. It uses DDR to achieve this purpose [4].

The UDP/IPv4 Ethernet stack has being designed for a 10/100/1000 Base-T Ethernet port with a specific development board that contains an RGMII chip. This chip is the one in

charge of interfacing with the FPGA stack protocols. Therefore, we are going to focus the explanation only on this type of interface.

## 2.2.2. Reduced gigabit media-independent interface (RGMII)

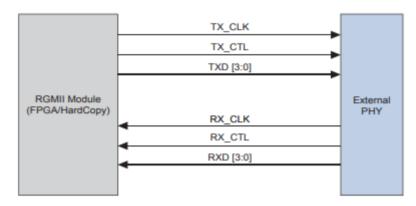

The RGMII is designed for 10/100/1000 Ethernet speeds with a reduced number of pins. It creates a transmit path from the media side to the physical side, and a receive path from the physical side to the media side. These are the supported speeds:

Table II. RGMII Ethernet supported speeds [4]

| RGMII supported Ethernet speeds |       |                  |  |  |  |  |  |  |  |  |

|---------------------------------|-------|------------------|--|--|--|--|--|--|--|--|

| [Mbits/s]                       | [MHz] | Bits/clock cycle |  |  |  |  |  |  |  |  |

| 10                              | 2.5   | 4                |  |  |  |  |  |  |  |  |

| 100                             | 25    | 4                |  |  |  |  |  |  |  |  |

| 1000                            | 125   | 8                |  |  |  |  |  |  |  |  |

RGMII uses half the number of data pins than older standards like GMII. The reduction of data pins is achieved by using both the rising and falling edge of the clock in a process called DDR (for 1000 Mbit/s operation) and by eliminating other signals that are not essential for a working interface. The RGMII has then 12 pins:

Table III. Minimum input and output ports needed in a RGMII for a working chip [4] [5]

| Signal  | I/O Type | Description                                                                                                                                              |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXC     | Output   | Transmit clock from an FPGA                                                                                                                              |

| TXD[30] | Output   | Data to transmit. Bits 3:0 on the positive edge of TX_CLK and bits 7:4 on the negative edge of TX_CLK.                                                   |

| TX_CTL  | Output   | Multiplexing of transmitter enable and transmitter error signals. TXEN on the positive edge of TX_CLK and TXEN xor TXERR on the negative edge of TX_CLK. |

| RXC     | Input    | Receive reference clock from the external PHY                                                                                                            |

| RXD[30] | Input    | Data to receive. Bits 3:0 on the positive edge of RX_CLK and bits 7:4 on the negative edge of RX_CLK.                                                    |

| RX_CTL  | Input    | Multiplexing data valid and receiver error. RXDV on the positive edge of RX_CLK and RXDV xor RXERR on the negative edge of RXC.                          |

The transmission clock signal is provided by the MAC on the TXC line. The RGMII standards say that data and clock have to be output at the same time (source-synchronous clocking) without any skew on the clock. For a correct sampling at the receiving side some delay has to be added to the clock (1.5-2ns), this can be done in the PCB design or at the receiver device as an internal delay.

Data is clocked in both clock edges for 1000Mbit/s but only in the rising edge for 10 and 100 Mbit/s. There is an exception to that: the signal RX\_CTL is in charge of transmitting RXDV (data valid) on the rising edge and RXDV xor RXER (receiver error) on the falling edge. In the other hand, TX\_CTL transmits TXEN (transmitter enable) on the rising edge and TXEN xor TXER (transmitter error) on the falling edge. This happens in the case of all three speeds. We will deepen into the operation of the RGMII in the design section.

### 2.3. Data link layer

This layer is in charge of delivering frames between different nodes on the same level of the network. The data link layer has two sublayers, the logical link control (LLC) and the media access control (MAC).

- Logical link control (LLC): The LLC is used to multiplex the protocols of the upper layer. It can perform more actions like flow control, error notification, acknowledgement, etc. It is defined in IEEE 802.2 [8].

- Medium access control (MAC): The medium access control sublayer (also known as media access control sublayer) also provides multiplexing and flow control, but in this case of the physical transmission medium. As it has already been explained, the MAC block is usually connected to the PHY via a MII block.

- When transmitting data, the MAC modify the frames into frames appropriate to the physical medium. It adds preambles for clock synchronism, padding, an FCS for error identification, etc. The MAC then sends the data when allowed. This sublayer is also responsible of retransmission of packets if congestion, collisions or jamming is found.

When receiving data, the MAC has to check the data integrity (with the CRC). It has to remove the preamble and padding too, before allowing the data to reach higher protocols [2].

The stack has been designed around the Ethernet protocol and the project has been created for a wired Ethernet connection. IEEE 802.3 [3] defines the physical layer and the media access control for wired Ethernet. In the other hand, the use of an LLC sublayer is mandatory for all IEEE 802 networks, but Ethernet is an exception to that.

#### 2.3.1. Ethernet protocol

Ethernet is a computer network protocol that is widely used in local area networks, metropolitan area networks and wide area networks. The protocol has grown over the years and now supports a large array of bit rates and distances. The protocol is defined in IEEE 802.3 [3].

The protocol was originally used next to coaxial cables, but nowadays it has evolved and it used twisted pairs and fiber optic too. Devices like switches, hubs, repeaters and bridges have improved its network capabilities and scalability.

The Ethernet protocol is used in the data link layer, as a part of the MAC sublayer. Ethernet as a protocol has its own frame format; it will be explained in the next subsection. The protocol does not have flow control, and it does not have set up an automatic repeat request system. If incorrect packets are detected, they can only be cancelled or not retransmitted forward. The protocol cannot retransmit packets; this job is left to higher layer protocols.

The *Ethertype* field of the Ethernet frame can be seen as an LLC identifier, as it is used for multiplexing of top layer protocols. As this field is not mandatory, some packets may not have an LLC identifier. They should then use an IEEE 802.2 LLC specific header after the Ethernet one to allow for multiplexing between higher layer protocols. There are several types of Ethernet but the most common used by the IP protocol is the Ethernet II frame or DIX frame that does not use LLC (it just uses the Ethertype field).

#### 2.3.1.1. MAC addresses

The addresses used in the MAC sublayer are called media access control addresses or MAC addresses. They are based on an early addressing system used in an early version of Ethernet.

The MAC address is a unique identifier that is assigned to each device. It is used for communicate inside the data link layer. MAC addresses are usually assigned at the time of manufacturing the device.

The address contains 6 bytes (48 bits), they are traditionally represented as a set of 12 hexadecimal numbers separated by a colon or a dash. The first six digits represent the manufacturer, the other six digits are an identification number for the device. Nowadays we also have 64-bit MAC addresses, protocols that use them like IPv6, usually translate the 48-bit MAC addresses to 64 bits.

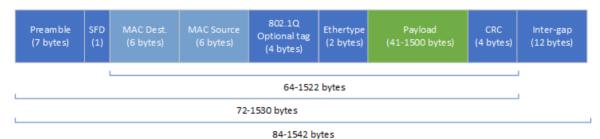

#### 2.3.1.2. Ethernet frame

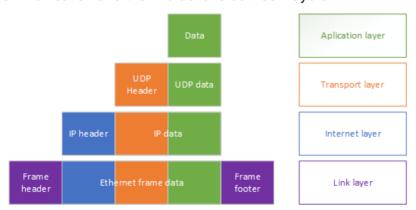

A typical Ethernet frame consists in two main parts: the frame and the payload [3]. The size of an Ethernet payload is of 1500 bytes; in some high-speed variants of the protocol, there is also the possibility to send jumbo frames that increases the limit up to 9000 bytes. The main parts of an Ethernet frame can be seen in Figure 4, we proceed with an explanation of each one of the fields:

Figure 4. Ethernet frame with minimum and maximum number of bytes [3]

• Preamble and Start frame delimiter (SFD): An Ethernet frame always starts with seven preamble bytes. The preamble is a pattern of alternating 1 and 0 bits (starting with a 1). It is used to synchronize the receiver clock of the devices on the network. This provides bit-level synchronization.

The SFD follows the preamble and it adds byte-level synchronization to the frame. The SFD is in charge of breaking the pattern of bits of the preamble to mark the start of the frame. SFD follows the following sequence: 10101011 (0xD5). It starts following the preamble pattern, but the last bit breaks it.

- Destination MAC address: This is the address of the device to which we are sending the packet. This address is sometimes unknown, so it may be necessary the use of address resolution protocols in the first place to discover the destination MAC.

- Source MAC address: The MAC address of the sender of the packet.

- EtherType: This field can represent two different things.

- o For values greater than 1536, it indicates the upper layer protocol (Network layer) that is encapsulated inside the payload. As an example, the IPv4 protocol it is a 0x0800 in the Ethertype field, and the ARP protocol 0x0806. Ethernet II frames use the field this way.

- For values between 0 and 1500 it represents the length of the payload in bytes, this is used for IEEE 802.3 frames [3], in this case, an IEEE 802.2 [8] LLC header will be added next to it as we still have the need for multiplex to the upper protocol.

- IEEE 802.1Q tag [6] or IEEE 802.1ad tag [7] (optional): These tags are used to indicate the existence of a VLAN membership. When in use the value of EtherType is changed to 0x8100 to indicate the change in frame format. The field has 16 bits that are divided in 3 subfields pointing out the class of service and frame priority level (3 bits), flag to indicate frames eligible to be dropped if congestion (1 bit) and the VLAN identifier (12 bits).

- Payload: The minimum payload is of 42 bytes with 802.1Q tag and 46 without it. If the payload is shorter than that padding is required. The maximum payload is 1500 bytes and more in jumbo frames.

- Frame check sequence (FCS): The FCS is a 32-bit cyclic redundancy check (CRC). It allows the receiver to detect corrupt data inside the frame (even a single bit). The FCS is computed using all the frame fields with the exception of itself (the FCS field).

- The FCS is complemented by the sender to avoid false negatives that could be generated by data with trailing zeroes. The complemented FCS will then give us a specific CRC32 residue as a correct result (Ex: 0xC704DD7B).

- End of frame: The end of frame is a symbol or sequence that indicates the end of the data stream at the physical layer. For Gigabit Ethernet its 8b/10b encoding uses special symbols that are transmitted before and after the frame is sent.

- **Interpacket gap:** This gap represents idle time between packets. After a packet is sent, it is mandatory for the transmitter to send at least 96 bits before the next packet.

#### 2.3.2. Address Resolution Protocol (ARP)

The Address Resolution Protocol (ARP) is a protocol used in communications to discover the link layer address of a device that is associated with an already given network layer address. This protocol is defined in IETF RFC 826 [9]

In the case of working with IPv4 over Ethernet, the ARP protocol will discover the MAC address of a specific system with the given IP associated with it. The ARP protocol is a very critical protocol in the Internet protocol suite, as IPv4 need that protocol to be able to transmit messages correctly. In IPv6 the NDP protocol replaces the ARP in this function.

The protocol uses a very simple format:

- Hardware type: Type of data link protocol in use Ex: Ethernet (4 bytes).

- Protocol type: Type of network protocol in use Ex: IPv4 (2 bytes).

- Hardware length: The length of a data link address (1 bytes).

- Protocol length: For the length of network layer addresses (1 byte).

- **Operation:** That specified the ARP operation we are performing (1 for request, 2 for reply) (2 bytes).

- Sender hardware address: The data link layer address of the sender.

- Sender protocol address: The network layer address of the sender.

- Target hardware address: The data link layer address of the intended receiver. (Empty in a request)

- Target protocol address: The network layer address of the intended receiver

The ARP has two modes of operation: Request and reply. In request, the sender is requesting the target hardware address of a specific target protocol address, during the consequent reply the target (now working as a sender) returns a message with the sender hardware address field filled with the requested answer. The targets field in this case point to the original requester. The size of an ARP message is variable and it mainly depends on the size of both types of addresses.

## 2.3.2.1. ARP cache

Addresses that are collected using the ARP protocol have to be stored somewhere. The ARP cache table is a repository used to store the data we gather using the protocol. In the ARP cache pairs of network layer addresses and data link layer addresses are stored and can be retrieved by the system when needed without the need of having to perform constant requests.

A system can work without an ARP cache, but adding one reduces greatly the network traffic, as the cache allows us to send a message to already matched devices without the need to request its hardware address every time.

Sometimes the IP of a device might change without notice, or even, another device can be assigned to an already cached MAC. In order to deal with this, the ARP cache has to renew its matched addresses when a certain amount of time passes (timeout), this time is variable and can be modified at the criterion of the designer. In addition, if a cache entry is not used for a specific time, it has to be removed from the cache, thus leaving space to entries of other devices that are being used at the moment.

An ARP cache can have static and dynamic entries. Static entries are manually added to the table and are permanent. Dynamic entries are added by the protocol normal operation and this are the ones that are only kept in the cache for a specific period.

## 2.4. Network layer

This layer groups the set of protocols in charge of transport network packets from a specific source to a destination host. This process can happen though one single network or multiple ones. Some of the functions of this layer are:

- Connectionless communication: There is no need of ACKs; connection-oriented communication is left to higher layers.

- Host addressing: There should be a system of identifiers in the network (ex: IP addresses).

- Message forwarding: To forward packets between different networks.

The main network protocol of our stack is the IP protocol, specifically it is used the IPv4 protocol. It is not necessary the use of IPv6, as the stack is designed for use in small or medium LAN networks that do not require that amount of addresses, and that are usually still using IPv4. The ICMP protocol is encapsulated inside IPv4, but it is not considered a transport protocol as it works as a complement to IP messages. Both protocols are explained below.

#### 2.4.1. Internet protocol version 4 (IPv4)

The internet protocol version 4 (IPv4) is the fourth version of the well-known internet protocol (IP). The internet protocol is a network layer protocol, made for CL-mode communication on packet-switched networks, each data unit is addressed individually, and it is routed based in the information found in itself, not in a prearranged information. The protocol works on a best-effort delivery; it does not provide any kind of guarantee that the data is delivered or that the delivery meets the required quality. The users will receive a variable bit rate, latency and packet loss depending on the traffic load. Some of the aspects mentioned here can be changed or improved using the correct transport layer protocol, for example the Transmission Control Protocol (TCP) is a connection-oriented transport protocol that can be used with IPv4, in the other hand if we want to keep the connection connectionless, we have other transport protocols like the User Datagram Protocol (UDP). The protocol is fully defined in IETF RFC 791 [10].

#### 2.4.1.1. Protocol header

An IP packet have a header section and a data one in Figure 5 we can see the structure of an IPv4 packet:

|         | IPv4 Header Format |    |                                       |   |   |   |   |   |   |   |          |    |   |        |        |     |          |          |               |      |    |      |      |      |        |    |    |    |    |    |    |    |       |

|---------|--------------------|----|---------------------------------------|---|---|---|---|---|---|---|----------|----|---|--------|--------|-----|----------|----------|---------------|------|----|------|------|------|--------|----|----|----|----|----|----|----|-------|

| Offsets | Octet              |    |                                       |   | ( | ) |   |   |   |   | 1        |    |   |        |        |     |          |          | 2             |      |    |      |      |      |        |    | 3  |    |    |    |    |    |       |

| Octet   | Bit                | 0  | 1                                     | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9        | 10 | 1 | 1   12 | 2   13 | 1   | 14   15  | 16       | 17            | 18   | 19 | 9 20 | ) 21 | 1 /2 | 22   2 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 31 |

| 0       | 0                  |    | Version IHL                           |   |   |   |   |   |   |   | DSCP ECN |    |   |        |        |     |          |          | Total Length  |      |    |      |      |      |        |    |    |    |    |    |    |    |       |

| 4       | 32                 |    | Identification Flags Fragment Offset  |   |   |   |   |   |   |   |          |    |   |        |        |     |          |          |               |      |    |      |      |      |        |    |    |    |    |    |    |    |       |

| 8       | 64                 |    | Time To Live Protocol Header Checksum |   |   |   |   |   |   |   |          |    |   |        |        |     |          |          |               |      |    |      |      |      |        |    |    |    |    |    |    |    |       |

| 12      | 96                 |    | Source IP Address                     |   |   |   |   |   |   |   |          |    |   |        |        |     |          |          |               |      |    |      |      |      |        |    |    |    |    |    |    |    |       |

| 16      | 128                |    |                                       |   |   |   |   |   |   |   |          |    |   |        | De     | est | tinatior | ı IP A   | Addı          | ress |    |      |      |      |        |    |    |    |    |    |    |    |       |

| 20      | 160                |    |                                       |   |   |   |   |   |   |   |          |    |   |        |        |     |          |          |               |      |    |      |      |      |        |    |    |    |    |    |    |    |       |

| 24      | 192                |    |                                       |   |   |   |   |   |   |   |          |    |   |        |        | ٥,  | ptions ( | if IL    | II <b>\</b> [ | 5١   |    |      |      |      |        |    |    |    |    |    |    |    |       |

| 28      | 224                |    |                                       |   |   |   |   |   |   |   |          |    |   |        |        | U   | puons    | , 11 111 | IL/           | رر   |    |      |      |      |        |    |    |    |    |    |    |    |       |

| 32      | 256                | L. |                                       |   |   |   |   |   |   |   |          |    |   |        |        |     |          |          |               |      |    |      |      |      |        |    |    |    |    |    |    |    |       |

Figure 5. Format of an IPv4 header with byte references [10] [11]

We are going to explain now all the parts that forms an IPv4 packet:

- **Version:** The IP packet version, for IPv4 this is always 4, for IPv6 [11] it will be 6.

- Internet header length (IHL): Size of the IP header. The length is calculated multiplying the value at IHL by 32 bits, the maximum value inside the IHL is 15 so: 15x32=480 bits.

- **Differentiated Services Code Point (DSCP):** This field specified differentiated services (DiffServ) by RFC 2474, 3168 and 3260. Differentiated services are mainly used to provide quality of service, for example low-latency to critical networks (streaming), best effort to non-critical ones.

- Explicit Congestion Notification (ECN): This field allows end-to-end notification

of network congestion without dropping of packets, this is an optional feature that

can only be used if both ends of the communication are willing to do it. It is defined

in RFC3268.

- **Total Length:** The entire packet size in bytes, it includes the header and all the data. The minimum size is 20 bytes (no data), and the maximum size is 65535 bytes. All host must be able to manage packets of at least 576 bytes.

- Identification: This field is used to identify the group of fragments of a single IP datagram.

- Flags: These three bits are used to control and identify fragments. The bit 0 is reserved, the bit 1 (Don't Fragment DF) forbids the fragmentation of the packet if it is set at '1' (if packet is too big it will be dropped). The bit 2 (More Fragments MF), for unfragmented packets the MF is '0', for fragmented packets all packets have that bit at '1' with the exception of the last one.

- Fragment Offset: This field is measured in units of eight-byte blocks. It specifies the offset that a particular fragment has regarding the original unfragmented packet. The first fragment has an offset of 0, and the maximum offset is set by the maximum data that can be sent with an IPv4 packet (65528 bytes of data).

- Time To Live (TTL): This field sets the datagram lifetime once sent. Its value is

decreased by one every time the packet hops to the next network device (it is also

called hop limit). When the field reaches a 0 the router discards the packet, and it

usually sends an ICMP Time Exceeded message to the sender.

- **Protocol:** Here we defined the protocol used in the upper layer (transport layer), for example UDP (17), TCP (6) or ICMP (1).

- Header Checksum: The checksum is the 16-bit one's complement of the one's complement sum of all 16-bit words of the header. When the checksum field is

considered zero during the calculation of it. It is used for error checking, when the packet arrives a router or device the checksum is calculated, if the checksum calculated does not match the one in this field the packet is discarded.

- Source Address: The IPv4 address of the sender of the packet.

- **Destination Address:** The IPv4 address of the receiver of the packet.

- Options: Not usually used.

#### 2.4.1.2. Fragmentation

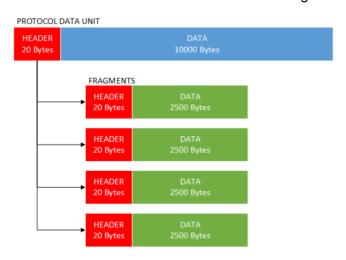

The protocol supports fragmentation, if we want to pass through a link a packet that is too big, the packet needs to be broken into smaller pieces and then reassembled by the host at the end. The maximum transmission unit (MTU) is the maximum size allowed in a link, if this size is lower than the packet length it has to be fragmented. Fragmentation of packets for IP is defined in RFC 791 [10] and the reassembly algorithm in RFC 815 [12]. As we have already seen the IPv4 header uses some of its fields for fragmentation.

Figure 6. Example of fragmentation of a Datagram [10]

When fragmenting each fragment of the original datagram will get its own fragment header, this new header contains the fragment offset corresponding to each fragment. All fragments with the exception of the last one will have the More Fragments flag set to '1'. The length field of the IP header will have the fragment length, and the checksum of each fragment is calculated for separated. The rest of the header is like the original one. The receiver end is in charge of the reassembly of the fragments in the correct order using the offset field, the reassembly can be also made by an intermediary.

#### 2.4.1.3. Protocol addresses

IPv4 uses 32-bit addresses, the total of possible addresses in a network is then ( $2^{32}$  = 4294967296). Addresses are usually represented as four decimal octets ranging from 0 to 255 and separated by dots. The addresses are divided in two main parts, first the network portion that is usually located in the first bits, secondly the host identifier that occupies the rest of the bits.

In the original design, the network number was the first (or highest) octet, but this method only allowed 256 networks, so it was quickly outdated [13]. New methods were created to increase the number of networks as the IP address exhaustion has being a critical problem

since the almost the beginning, as the original design did not have enough capacity. Things like mobile devices and the rapid growth of the internet all over the world aggravated the problem.

In 1981 classful networking was created to try to extend this limit [10]. This system defined five classes from A to E. Classes A, B and C had different bit lengths for network identification, the rest of the address was used as previously to identify the host. Class D was defined for multicast and Class E was reserved for the future.

Later on, Classless Inter-Domain Routing (CIDR) replaced the system of classes. CIDR is a standard that eases the routing by having blocks of addresses grouped into routing table entries [14].

CIDR uses variable-length subnet masking (VLSM) to assign IP addresses to subnets depending on the need of each one of them. The division between the network and the host can happen in any of the 32 bits that an IP address has. Subnet masking uses a combination of bits to delimitate a network, its main function is to tell to devices which part of the IP address is the network and which one the host.

The address groups are called CIDR blocks and share a sequence of bits in their IP addresses representations. The blocks are identified with a similar format than IP addresses with four decimal octets separated by a dot and a slash at the end followed by a number from 0 to 32.

The first numbers are interpreted like an IP address, the slashed number is the length of the prefix, counting from the left it represents the number of common bits in all addresses. To read the CIDR address correctly, we need to represent the address in binary.

### 2.4.2. Internet Control Message Protocol (ICMP)

The Internet Control Message Protocol or ICMP is a support protocol of the Internet Protocol. The ICMP complements the IP Protocol with a range of options, it is used by network systems and devices to send error messages and other types of information like when a service is not available, or a device cannot be reached, etc. The ICMP protocol formal definition can be found in RFC 792 [15].

ICMP messages are normally used for control or diagnostic. It is also used as a response to errors in IP operations as specified in RFC 1122 [1]. Some of the possible applications that the ICMP messages have are for example: pings, time exceeded messages, traceroute commands, destination unreachable messages, router solicitation and advertisement, etc.

ICMP uses the IP like an upper layer protocol, but ICMP actually behaves as an integral part of the IP protocol. ICMP is a network layer protocol, so it does not have a port number associated.

|         | ICMP Header Format |                 |                       |                         |                         |  |  |  |  |  |  |  |

|---------|--------------------|-----------------|-----------------------|-------------------------|-------------------------|--|--|--|--|--|--|--|

| Offsets | Octet              | 0               | 1                     | 2                       | 3                       |  |  |  |  |  |  |  |

| Octet   | Bit                | 0 1 2 3 4 5 6 7 | 8 9 10 11 12 13 14 15 | 16 17 18 19 20 21 22 23 | 24 25 26 27 28 29 30 31 |  |  |  |  |  |  |  |

| 0       | 0                  | Type            | Code                  | ksum                    |                         |  |  |  |  |  |  |  |

| 4       | 32                 | Rest of Header  |                       |                         |                         |  |  |  |  |  |  |  |

Figure 7. Format of ICMP header [15]

The ICMP works using the IPv4 protocol, in the IP header it is identified as the protocol number '1'. All the ICMP packets are made by an 8-byte header and a data section of variable size. The first byte of the header is reserved for the type of ICMP message, the second byte called code specifies an ICMP subtype. The third and fourth bytes are a checksum. The next bytes are of variable size and content, depending on the type and code we want to send. It is important to notice ICMP error messages maximum length is 576 bytes.

ICMP control messages are specified by the type and code fields. The code field is used to give a context to the message. Since the introduction of the protocol some control messages have been deprecated and are no longer available to use. Here we have an example of the most used ones:

Table IV. Example of some ICMP control messages [15]

| Message name            | Туре | Code | Description                       |  |  |  |  |  |  |

|-------------------------|------|------|-----------------------------------|--|--|--|--|--|--|

| Echo Reply              | 0    | 0    | Echo reply (used to answer ping)  |  |  |  |  |  |  |

| Destination Unreachable | 3    | 0    | Destination network unreachable   |  |  |  |  |  |  |

|                         |      | 1    | Destination host unreachable      |  |  |  |  |  |  |

|                         |      | 2    | Destination protocol unreachable  |  |  |  |  |  |  |

|                         |      | 3-15 | Others                            |  |  |  |  |  |  |

| Echo Request            | 8    | 0    | Echo request (used to ask ping)   |  |  |  |  |  |  |

| Time Exceeded           | 11   | 0    | TTL expired in transit            |  |  |  |  |  |  |

|                         |      | 1    | Fragment reassembly time exceeded |  |  |  |  |  |  |

## 2.5. Transport layer

The transport layer is set to provide host-to-host communication. This layer can implement many functions, like connection-oriented communications, flow control or multiplexing of higher layer protocols (applications or services). It is the layer with a highest focus on reliability. Its main functions are:

- **Connection-oriented communication:** TCP is known for having it. UDP is an alternative transport protocol that is actually still connection-less.

- Same order delivery: The network layer does not guarantee that this is solved here

- Reliability: Error detection techniques, acknowledgements, automatic repeat request schemes, etc. In order to avoid the loss of packets during network congestions or other issues.

- Flow control: Control between two nodes to prevent a sender that is too fast for the receiving buffer.

- Congestion control: To avoid the collapse of the network. Things like reducing the rate of sending packets, and slow-start, etc.

- Multiplexing: The option to multiplex between the higher layer nodes is available thanks to ports.

The most used protocol at the transport layer in the Internet suite is the TCP, despite that, the stack has been designed putting speed in front of reliability, and this make it preferable to use the UDP protocol. Both protocols are going to be explained next, but the focus will be in the UDP protocol, as it is where we have the real interest.

#### 2.5.1. User Datagram Protocol (UDP)

The User Datagram Protocol or UDP is one of the two main transport layer protocols used in the internet protocol suite. It is formally defined in RFC 768 [16]. It is a transport protocol that is usually used as an alternative to TCP. UDP uses a connectionless communication model, it has checksums for data integrity and it uses port numbers as a way for addressing messages in the device. It does not have handshakes so it is exposed to unreliability, there is not guarantee of delivery, ordering or duplicate protection.

If we are looking for error checking, error-correction and reliability using TCP is recommended. UDP is usually used for time-sensitive applications and real time systems as it is more important the speed of the transmission (not waiting times, not retransmission), and the drop of packets can be allowed.

#### 2.5.1.1. Protocol Header

| UDP Header |       |                 |             |  |  |  |  |   |   |    |    |    |    |    |    |    |                         |  |  |  |      |               |    |    |                   |  |  |  |  |    |

|------------|-------|-----------------|-------------|--|--|--|--|---|---|----|----|----|----|----|----|----|-------------------------|--|--|--|------|---------------|----|----|-------------------|--|--|--|--|----|

| Offsets    | Octet | 0               |             |  |  |  |  |   | 1 |    |    |    |    |    | 2  |    |                         |  |  |  | 3    |               |    |    |                   |  |  |  |  |    |

| Octet      | Bit   | 0 1 2 3 4 5 6 7 |             |  |  |  |  | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 16 17 18 19 20 21 22 23 |  |  |  |      | 23            | 24 | 25 | 26 27 28 29 30 31 |  |  |  |  | 31 |

| 0          | 0     |                 | Source port |  |  |  |  |   |   |    |    |    |    |    |    |    |                         |  |  |  | Des  | tination port |    |    |                   |  |  |  |  |    |

| 4          | 32    | Length          |             |  |  |  |  |   |   |    |    |    |    |    |    |    |                         |  |  |  | Chec | ksur          | n  |    |                   |  |  |  |  |    |

Figure 8. Standard format of UDP header [16]

- **Source port:** The sender's port number, assumed to be the port where we should reply. If the field is not used, it should be 0.

- Destination port: The receiver's port. This port is mandatory, in our system each service has a port assigned and is in charge of tell the stack when a message is directed to it.

- Length: The length in bytes of the UDP header and the UDP data. The minimum length is 8 bytes (only header), the maximum length is 65507 bytes (65535 8 UDP header 20 IP header).

- **Checksum:** The UDP checksum for error-checking, the field is optional for IPv4 (set to 0 if not used). The UDP protocol is calculated with the UDP header, the data and an IPv4 pseudo header.

#### 2.5.1.2. Ports

UDP ports are 16-bit integer numbers (between 0 and 65635). Ports are used to multiplex the messages between all the services and applications linked to a specific IP address

(assigned to a specific device). Port 0 is reserved, but it is allowed as a source port value if the sender is not expecting a reply.

## 2.5.1.3. Checksum computation

The UDP checksum is calculated by the 16-bit one's complement of the one's complement sum of the UDP header, the data and a IP pseudo-header, all padded with "zero" bytes at the end (if necessary) to make it a multiple of two bytes.

If the network protocol is IPv4 (as in our stack), the pseudo header computed has to be formed by the Source IPv4 Address, the destination IPv4 Address, a byte of zeroes, the protocol field, and the UDP length (notice that this length is asked again in the UDP header).

### 2.5.2. Transmission Control Protocol (TCP)

The TCP protocol is the other main protocol of the Internet model (also called TCP/IP model). The protocol is defined in RFC 793 [17]. It is the completely opposite than UDP in most of its features.

TCP It is characterized for being a very reliable protocol, it provides error detection and retransmission of wrong packets, flow and congestion control, acknowledgments, handshakes and the most important feature; it is connection-oriented, TCP requires three packets to create a connection. It can rearrange the packets in the correct order. TCP is slower than UDP but more reliable, we are guaranteed to receive the packets.

## 2.6. Application layer

In this last section, we have what we called application layer, here we have joined the session, presentation and application layers of the OSI model. This last layer groups the protocols in charge of process-to-process communication.

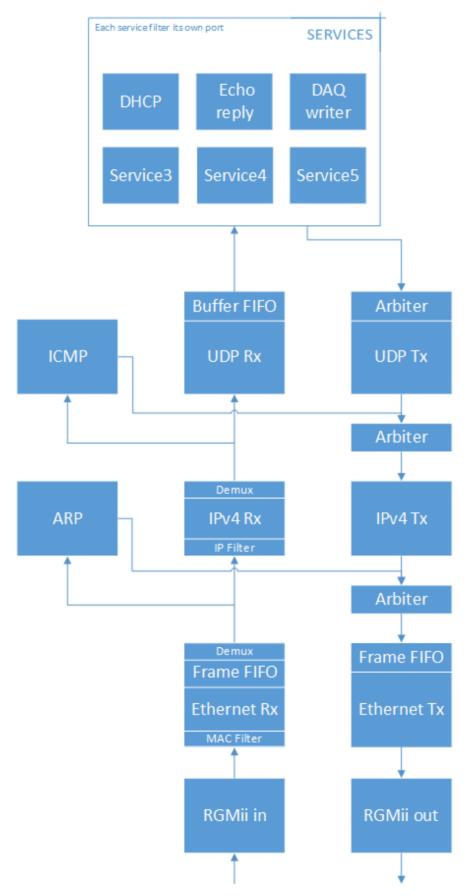

Here we will describe all the services that will use our designed stack to transmit and receive data. In the design, services of the application layer are created as separated IP cores that will be then connect to the UDP/IP stack for its use. The only exception to that is the DHCP protocol.

The DHCP protocol is necessary for a good performance of the stack inside network, this protocol is an integral part of the stack IP core. The stack has been designed for an easy use inside a non-controlled network, it should be "plug and play". This makes DHCP a mandatory protocol, as we do not want the need to configure the addresses of the devices we are connecting.

## 2.6.1. Dynamic Host Configuration Protocol (DHCP)

The Dynamic Host Configuration Protocol (DHCP) is a protocol of the application layer that is used to manage an UDP/IP network, it is derived from the older bootstrap protocol (BOOTP). They are both defined in RFC 2131 for DHCP [18] and RFC 951 for BOOTP [19].

The DHCP protocol is used to assign IP addresses and other network parameters to each network device, and to each new device that joins the network. This allows the devices to communicate with themselves and other networks. A DHCP Server is the one in charge of assigning these parameters and addresses to all the DHCP clients, usually the DHCP Server is located at the router.

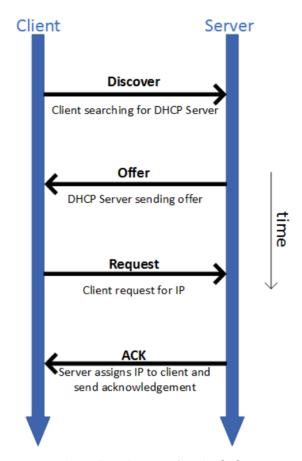

A typical DHCP session consist in four steps as seen in Figure 9: First the client (the device) sends a Discover broadcast to the network, the discover is searching for DHCP servers on the network, the servers that receive the discover message will answer with an IP offer, during the discovery phase the client can ask for more information about the servers like; server IP address, subnet mask, domain name, etc. all this info will be provided by the server's offer.

Figure 9: DHCP protocol session [18].

Once the offer has been received the client will take the offered IP and additional information and it will broadcast a Request of that IP address. If the server is ok with that request it will answer with an ACK message and the address will be assigned to that specific client, if the request is rejected the server will send a NACK answer and the client will have to request for a different IP.

The IP address will stay assigned to the client for a time specified in the ACK message. The IP lease time will be chosen by the server, typically the DHCP lease time default setting in most servers is 24 hours. Servers should try to avoid setting the lease time too low as this can cause interruptions to service.

### 2.6.1.1. DHCP header and options

The DHCP header is the same in all the messages, changing just the values of some field and the last field (Options) we are able to send all kind of DHCP messages (discovery, request, offer, ack, nack, etc...), these are the fields of a DHCP packet:

- Opcode (1 byte): Distinguish between a client request (0x01) message and a server reply (0x02)

- Hardware type (1 byte): Specifies the used network architecture, for example if set to 0x01 it will represent an Ethernet network.

- Hardware address length (1 byte): Represents the length of the hardware address. For Ethernet the length of a MAC address (48 bits).

- Hop count (1 byte): Number of relay agents that the message has passed.

- Transaction ID (4 bytes): ID number that identifies the client request and it is used to match request with replies.

- **Number of seconds (2 bytes):** Time that has passed since the client has started the DHCP process.

- Flags (2 bytes): If set to '1' it will mean that all replies have to be broadcast to the client.

- Client IP address (4 bytes): The client's IP address, once it has been confirmed, if the client still doesn't have an IP this field is set to all zeroes.

- Your IP address (4 bytes): The IP offered by the server to the client.

- Server IP address (4 bytes): IP of the next server the client has to contact to follow the configuration process.

- Gateway IP address (4 bytes): Relay agent IP address, filled by the relay agent if some exists.

- Client hardware address (16 bytes): Client hardware address (MAC address). It may require padding with zeroes to fill the 16 bytes.

- Server name (64 bytes): Optional server host name.

- File (128 bytes): Optional boot file name.

- Magic cookie (4 bytes): This field identifies the mode in with the next set of data will be interpreted. For DHCP the magic cookie must be 63.82.53.63 in hexadecimal.

- **DHCP options (Variable):** That field contains the data of the DHCP packet, a client must be prepared to receive options of at least 312 bytes (total message of 576 bytes). DHCP options are a set of custom configuration parameters and control information that can be added in the last field of a DHCP packet [20].

The Options field is the most critical of the packet, in there we will make our data requests to the DHCP server, and we will retrieve most of the information of the replies. All options begin with a tag byte that identifies the option, then for options with variable length it follows a length field, this length field doesn't include the tag and length fields itself, only the option data that will follow next. We can find some of the most important options in the following Table V. Some of the most common DHCP options, most of them used in the design of the project [20].. The option field ends when the option with code 255 is found, this option marks the end of the field and packet.

Table V. Some of the most common DHCP options, most of them used in the design of the project [20].

| Option Name               | Code | Length   | Description                                                                                                            |  |  |  |  |  |  |

|---------------------------|------|----------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pad Option                | 0    | Fixed    | It can be used to align other fields                                                                                   |  |  |  |  |  |  |

| End Option                | 255  | Fixed    | Marks the end of the options, it can be followed by padding (pad option).                                              |  |  |  |  |  |  |

| DHCP Message type         | 53   | Variable | Identifies the type of DHCP message.<br>Discovery, 2 Offer, 3 Request, 4 Decline,<br>ACK, 6 NACK, 7 Release, 8 Inform. |  |  |  |  |  |  |

| Client Identifier         | 61   | Variable | Identifies a DHCP client, it usually has the hardware type and address.                                                |  |  |  |  |  |  |

| Parameter<br>Request List | 55   | Variable | Used by the client to request a list o configuration parameters. (Subnet Mask Domain Name, Router, etc.)               |  |  |  |  |  |  |

| IP Address Lease<br>Time  | 51   | Variable | In discovery and request it allows to request a lease time, in offer it shows its offered value. (time in seconds)     |  |  |  |  |  |  |

| Domain Name               | 15   | Variable | Domain name for DNS                                                                                                    |  |  |  |  |  |  |

| Subnet Mask               | 1    | Variable | Specified the client's subnet mask                                                                                     |  |  |  |  |  |  |

| Requested IP<br>Address   | 50   | Variable | Used in Discovery or Request to request a particular IP.                                                               |  |  |  |  |  |  |

#### 2.6.2. Other services

We can add any number of services to the stack, the stack was mainly designed to read data from a DAQ block and sent the data to another host of the network. The DAQ is an example of a service block. Another service that have been suggested is an SPI interface for the configuration of ICs or other electronics. Some testing services have been created for the design, for example an echo block that returns the same message that we sent to it. This service only has the purpose of testing the design and testing that the connection between host and processes is correct (with a ping we are only testing the network layer).

## 2.7. Existing implementations

Some already existing implementations can be found with similar applications. Some companies have released IP cores with similar characteristics (or even more) but they were directly discarded for its high prices (more than 4000\$ for the IP core without extra protocols). One great example of that is the UDP/IP Ethernet IP core of Enclustra [21]:

- It has 1Gb/s, 100Mb/s and 10 Mb/s operations

- UDP, IPv4 and Ethernet protocols

- ARP protocol

- It works with MII, RMII, GMII and RGMII interfaces

- Destination UDP port, IP address and MAC address filtering

- UDP checksum generation and check, Ethernet CRC too

- Multiple UDP ports with dedicated Rx and Tx interfaces for each one.

In the territory of the open code we can find one remarkable core called 1G eth UDP/IP Stack and provided by Peter Fall and the FIXQRL project [22], it has the following remarkable characteristics:

- UDP, IPv4 and Ethernet protocols

- ARPv2 protocol with cache of multiple slots

- Separate clock domains for Tx and Rx

- UDP ports user filtering

- AXI interface to connect MAC core.

- It uses the Xilinx's MAC interface.

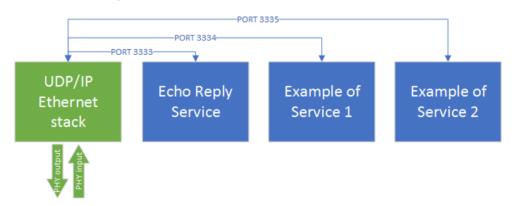

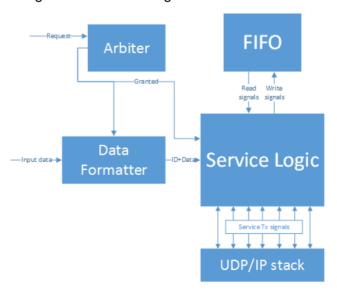

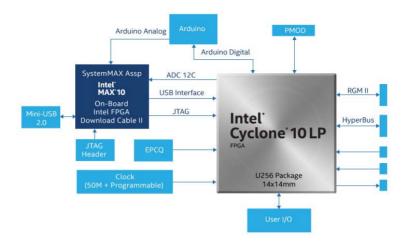

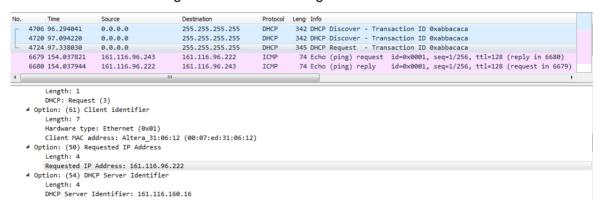

This solution is good but it is not very customizable, it does not have implemented a good system to increase its number of protocols in the different layers and a few protocols are missing like DHCP or ICMP. It is also designed specifically to be used with an AXI interface at its input.